请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TDA4VP-Q1 工具与软件:

尊敬的 TI 专家:

我们遇到了我们的供应商 Tanya 报告的 DDR 在2.1GHz 时的一个问题、即 DRAM2处的 CA 偏差线。 此问题似乎特定于 DRAM2、因此 DRAM1在相同频率下未观察到任何问题。 以下是有关情况的摘要:

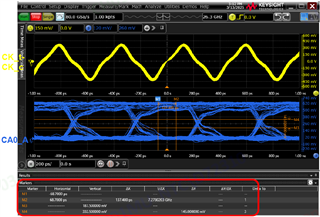

Tanya 已完成了4267Mbps 的测量、并观察到 DRAM2上存在 CA 线路偏移、该 CA 线路偏移可能微不足道、在 DRAM1上也不可见。

DRAM1和 DRAM2之间的 CA 存在差异。

Tanya 建议调整 DRAM2上的 CA 延迟来解决此问题、特别是将 CA 信号拉入50ps 至100ps、使 DRAM1和 DRAM2在行为上更加相似。

DRAM 1:

DRAM 2:

我可以问是否有任何方法可以调整 DRAM2上的 CA 偏差?

DDR 配置(2133MHz)(更改后缀):