主题中讨论的其他器件:ADS127L11、

工具/软件:

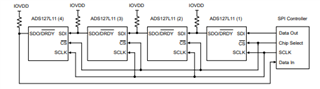

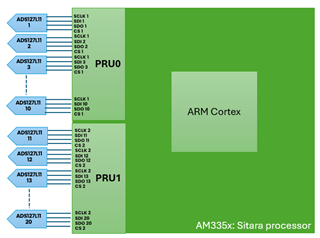

我们希望将20个 ADS12L11 ADC 连接到 Sitara 处理器的 PRU。

我们希望在上述采用并行采样的架构中实现100ksps 的采样率。 您能否告诉我们、这种方法是否可行?

为了在未来范围内保持额外的处理能力、我们考虑使用 AM64xx Sitara。 但是、AM64x 是否支持 QNX?

AM64x 还支持四核 cortex R5F 和双核 cortex A53。 那么、是否可以在 R5F 上运行 QNX 和在 A53上运行 Linux? 有人使用这种方式?

谢谢、此致、

Dnyandeep