工具/软件:

您好:

我们尝试使 J784S4 EVM 的两个 PCIe 端口都能在4x 中工作、但遗憾的是、我们无法 ATM。

此处的设置:

- 2个 J784S4XEVM:

- 第一个(EVM #A)在 RC 中配置了两个 PCIe 端口。

- 第二个(EVM #B)在 EP 中配置了两个 PCIe 端口。

- EVM #A 端口1之间的一个线束连接到 EVM #B 端口0。

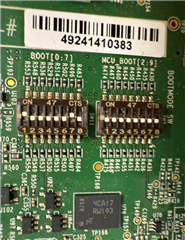

- SW11设置为100000010。

- SW7设置为00000000。

- SW2设置为100001101。 (RC 中的两个 PCIe 端口)。

- Linux SDK 版本:10.01.00.05。

在 EVM #A 上进行硬件修改以避免使用 USB、但应改为使用2个 PCIe 通道:

- 组装的组件:

- C696、C697。

- C683、C684。

- R891、R892。

- R876、R877。

- R168、R169。

- C125、C129。

- 未组装的元件:

- C694、C695。

- C679、C680。

- R885、R886。

- R867、R868。

- R170、R171。

- R152、R155。

软件修改:

- k3-j784s4-evm.dts:

diff --git a/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts b/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

index 56a037532..dd92863be 100644

--- a/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

+++ b/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

@@ -13,7 +13,7 @@

/ {

compatible = "ti,j784s4-evm", "ti,j784s4";

- model = "Texas Instruments J784S4 EVM";

+ model = "Texas Instruments J784S4 EVM (PCIe1 4X)";

chosen {

stdout-path = "serial2:115200n8";

@@ -458,13 +458,6 @@ J784S4_IOPAD(0x010, PIN_INPUT_PULLUP, 8) /* (AH33) MCAN13_RX.I2C4_SDA */

>;

};

- main_usbss0_pins_default: main-usbss0-default-pins {

- bootph-all;

- pinctrl-single,pins = <

- J784S4_IOPAD(0x0ec, PIN_OUTPUT, 6) /* (AN37) TIMER_IO1.USB0_DRVVBUS */

- >;

- };

-

main_mcan4_pins_default: main-mcan4-default-pins {

pinctrl-single,pins = <

J784S4_IOPAD(0x088, PIN_INPUT, 0) /* (AF36) MCAN4_RX */

@@ -1372,40 +1365,6 @@ &dss {

<&k3_clks 218 22>;

};

-&serdes0 {

- status = "okay";

-

- serdes0_usb_link: phy@3 {

- reg = <3>;

- cdns,num-lanes = <1>;

- #phy-cells = <0>;

- cdns,phy-type = <PHY_TYPE_USB3>;

- resets = <&serdes_wiz0 4>;

- };

-};

-

-&serdes_wiz0 {

- status = "okay";

-};

-

-&usb_serdes_mux {

- idle-states = <0>; /* USB0 to SERDES lane 3 */

-};

-

-&usbss0 {

- status = "okay";

- pinctrl-0 = <&main_usbss0_pins_default>;

- pinctrl-names = "default";

- ti,vbus-divider;

-};

-

-&usb0 {

- dr_mode = "otg";

- maximum-speed = "super-speed";

- phys = <&serdes0_usb_link>;

- phy-names = "cdns3,usb3-phy";

-};

-

&serdes_wiz4 {

status = "okay";

};

- k3-j784s4-main.dtsi:

diff --git a/arch/arm64/boot/dts/ti/k3-j784s4-main.dtsi b/arch/arm64/boot/dts/ti/k3-j784s4-main.dtsi

index 105a8fd39..69e7e5a6d 100644

--- a/arch/arm64/boot/dts/ti/k3-j784s4-main.dtsi

+++ b/arch/arm64/boot/dts/ti/k3-j784s4-main.dtsi

@@ -159,8 +159,8 @@ serdes_ln_ctrl: mux-controller@4080 {

<0x28 0x3>, <0x2c 0x3>; /* SERDES2 lane2/3 select */

idle-states = <J784S4_SERDES0_LANE0_PCIE1_LANE0>,

<J784S4_SERDES0_LANE1_PCIE1_LANE1>,

- <J784S4_SERDES0_LANE2_IP3_UNUSED>,

- <J784S4_SERDES0_LANE3_USB>,

+ <J784S4_SERDES0_LANE2_PCIE1_LANE2>,

+ <J784S4_SERDES0_LANE3_PCIE1_LANE3>,

<J784S4_SERDES1_LANE0_PCIE0_LANE0>,

<J784S4_SERDES1_LANE1_PCIE0_LANE1>,

<J784S4_SERDES1_LANE2_PCIE0_LANE2>,

下面是我们启用 EVM #B 后获得的结果:

和链接大写和状态:

我们遗漏了什么?