主题中讨论的其他器件: SysConfig、 DRA821

工具/软件:

尊敬的 Champ:

客户使用的是 DRA821U EVM、SOM 模块为 J7200XSOMG01EVM

Linux SDK 10.01.08.01

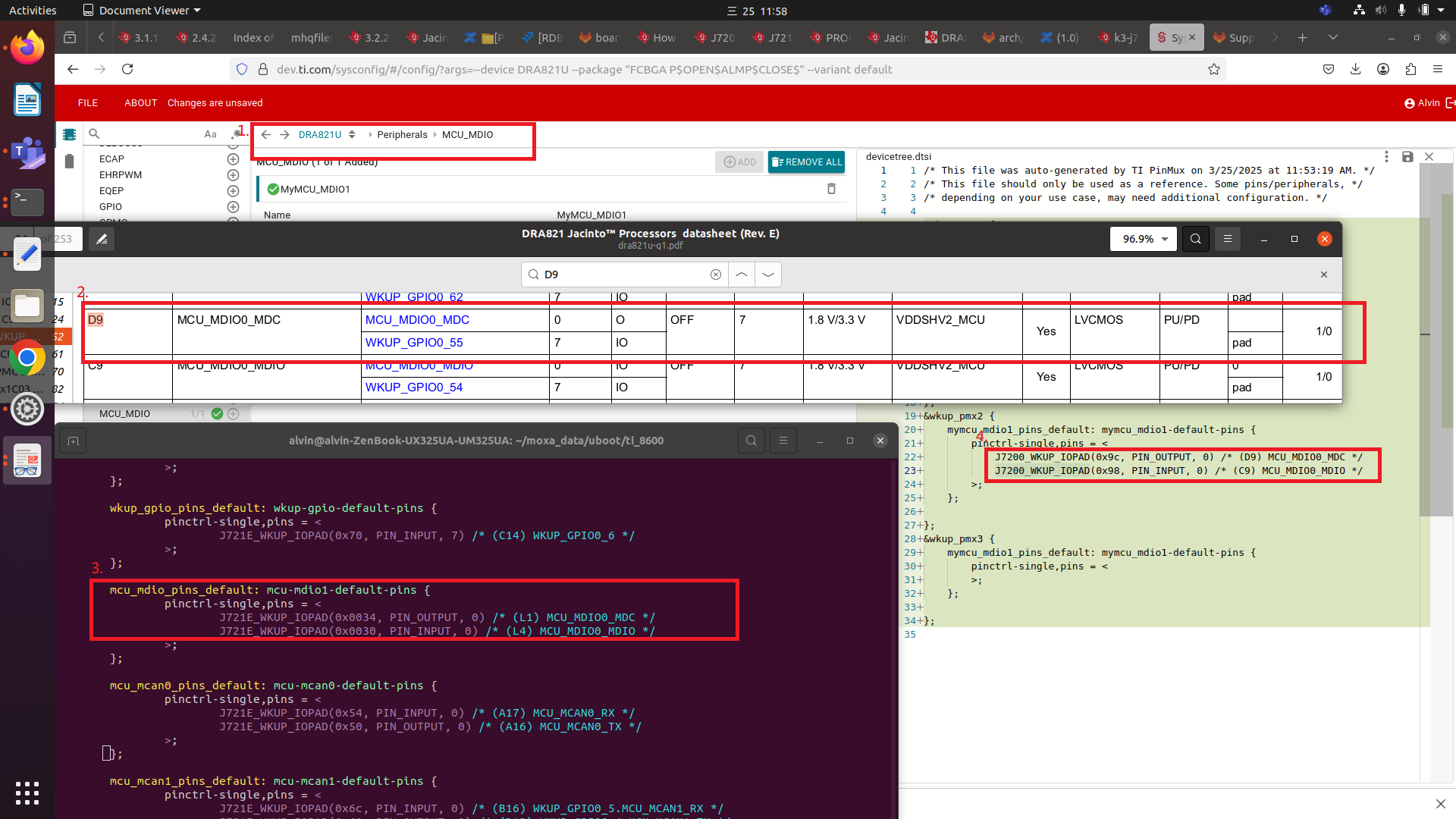

在 SDK 中、 j7200 arch/arm/dts/k3-j7200-common-proc-board.dts 将使用"J721E_WKUP_IOPAD"定义、MCU_MDIO0_MDC 和 MCU_MDIO0_MDIO 使用偏移0x34和0x30、注释分别显示引脚 L1和 L4。

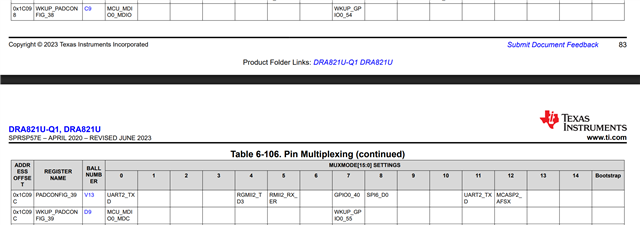

不过、数据表中的 DRA821U MCU_MDIO0是引脚 D9和 C9。

通过使用 SysConfig 生成 DTS、将创建"J7200_WKUP_IOPAD"中的所有引脚定义、这两个引脚的偏移为0x9C 和0x98。 (我无法映射 TRM 的 PADFx 的寄存器偏移地址和引脚、它不能指定哪个引脚(焊球)映射到 PADCONFx。)

我们只能选择相信 sysconf、但现在客户会感到困惑、无法将 DTS 重新用于 SDK 原始器件树。

辅助器件、客户尝试将 MCU_MDIO_PINS_DEFAULT 引脚修改为正确的引脚、但发现 MDIO 在更改到正确的引脚后不工作。

当前设置似乎正确、但我们目前无法判断正在使用哪些引脚。

EVM 硬件使用引脚 D9和 C9作为 sysconf 工具所示。

客户想知道在自己的电路板准备就绪后如何设置这两个引脚。

请帮助

1.检查缺少什么以及哪个设置正确。

2.从何处获取 DRA821每个引脚的 PADF 寄存器偏移映射。

Br、Rich

- SysConfig 的 Devive 是選 DRA821U?

- 使用sysconfig 產出的 dtsi 與 MCU_MDIO 中 SDK 上敘述的 j7200 arch/arm/dts/k3-j7200-common-proc-board.dts 腳位對不上

- 有確切的 reference menu 的devive 嗎 sysconfig 跟對應?? EVM 上的型號是 J7200XSOMG01EVM