工具/软件:

您好、专家、

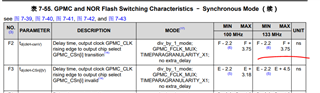

我们讨论的是 GPMC 突发模式。 但我们发现信号具有容差:

- GPMC_CLK、 0.475P - 0.3 (ns)

- GPMC_CS: 最小:F - 2.2、最大:F + 3.75

- GPMC_AD[n:0]:最小:j - 2.3、最大:j + 2.7

您能帮助澄清以下问题吗?

1)信号偏差与什么有关?

2)信号容差是否与不同的 AM64x 芯片相关?

3)信号容差是固定的还是随机的?

4)该信号 GPMC_CS 的容差太大、在133MHz 时、信号的容差范围大于周期的70%(GPMC_CLK)。