主题:DP83869中讨论的其他器件

工具/软件:

尊敬的专家:

SDK:ti-processor-sdk-linux-adas-j722s-evm-10_00_00_08

DTS:

&cpsw3g {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&rgmii1_pins_default>;

};

&cpsw3g_mdio {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&mdio_pins_default>;

cpsw3g_phy0: ethernet-phy@0 {

reg = <0>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

ti,min-output-impedance;

};

cpsw3g_phy1: ethernet-phy@1{

reg = <1>;

ti,op-mode = <DP83869_SGMII_COPPER_ETHERNET>;

};

};

&cpsw_port1 {

phy-mode = "rgmii-rxid";

phy-handle = <&cpsw3g_phy0>;

};

&cpsw_port2 {

status = "okay";

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&serdes1_sgmii_link>;

phy-names = "serdes";

phy-handle = <&cpsw3g_phy1>;

};

&serdes_ln_ctrl {

idle-states = <J722S_SERDES0_LANE0_USB>,

<J722S_SERDES1_LANE0_QSGMII_LANE1>;

};

&serdes0 {

status = "okay";

serdes0_usb_link: phy@0 {

reg = <0>;

cdns,num-lanes = <1>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_USB3>;

resets = <&serdes_wiz0 1>;

};

};

&serdes1 {

serdes1_sgmii_link: phy@0 {

reg = <0>;

cdns,num-lanes = <1>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_SGMII>;

resets = <&serdes_wiz1 1>;

};

};

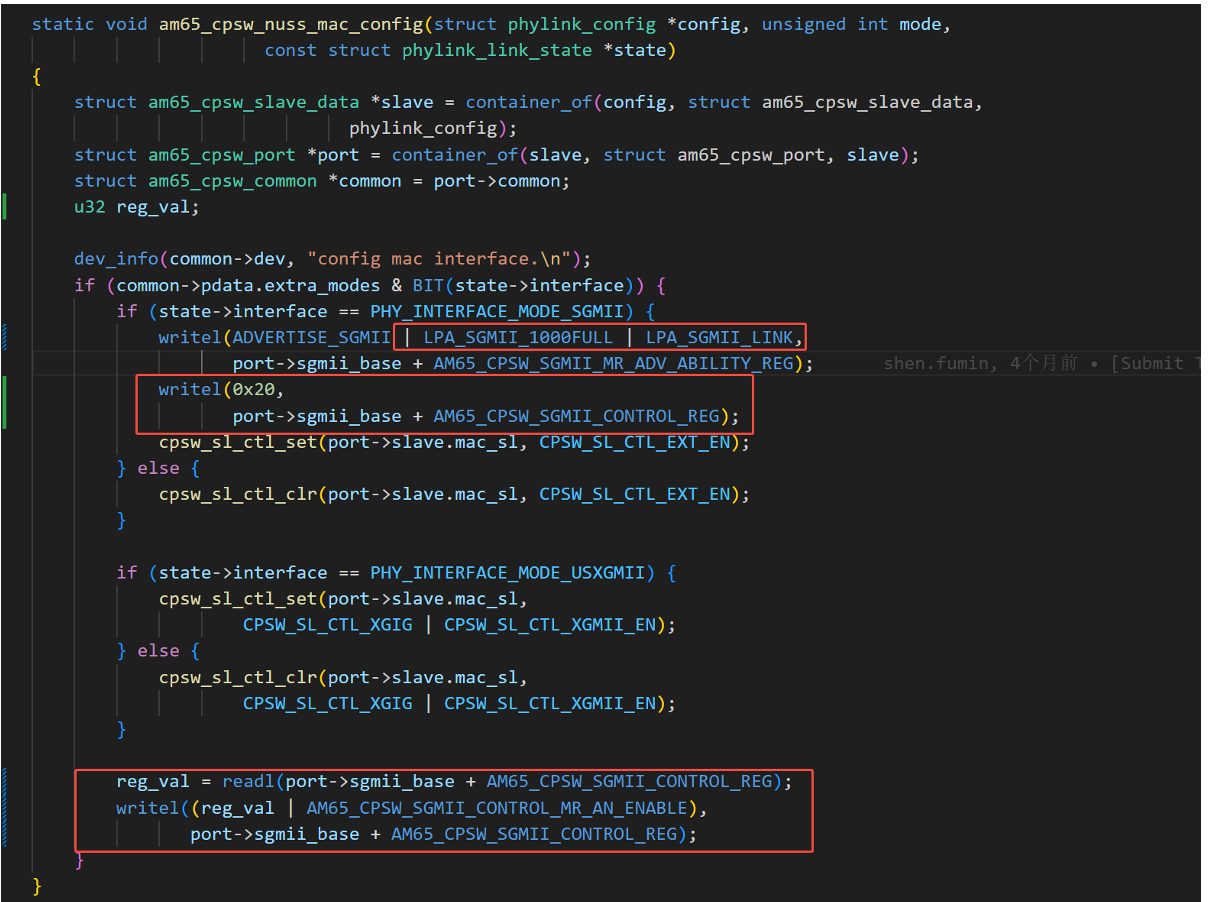

我们有一个需要使用双网卡的 TDA4VEN 项目。 我们在 SerDes1上安装了一个带有 SGMII 接口的 Rtl8211FS 网卡。

此 DTS 的配置无法正确加载 SGMII RLK8211fs 的 phy 驱动程序。 我可以询问如何配置它

谢谢你。