工具/软件:

香榭丽舍大街

AM67x PCIe 有三个勘误表。

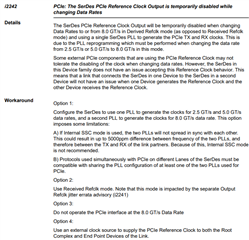

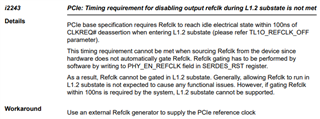

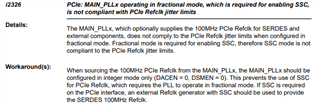

I.2242、I.2243和 I.2326

对于 I.2242、如果客户声称仅支持 PCIe 第2代(不支持第3代、8Gbps)、则他们想知道是否可以使用 AM67x 生成的时钟源。 客户也不会使用 PCIe Gen 3器件。

目的是不使用外部源时钟进行生产、以节省成本。

对于 I.2243和 I.2326、一个用于时钟门控、另一个用于 PCIe SSC 支持。

如果不考虑这两项、我们是否建议为 PCIe 添加外部源时钟? (I.2242的备选案文4)

由于客户正在进行 PCB 修改、并需要决定是否添加外部100Mhz 时钟源、因此请尽快对此进行评论。

Br、Rich