工具/软件:

您好:

我想确认哪些信息是正确的。

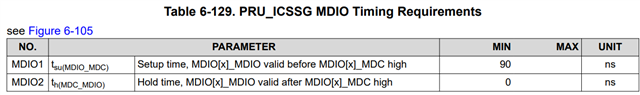

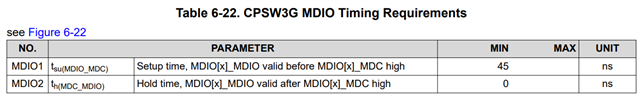

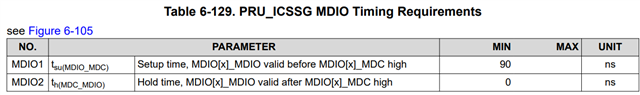

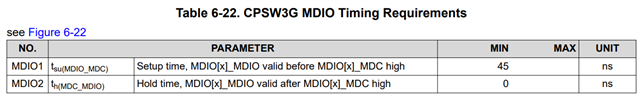

*根据数据表,有以下两个规格。

从数据表中、我知道 MAC 侧的 MDIO 读取值基于 MDC 上升沿锁存。

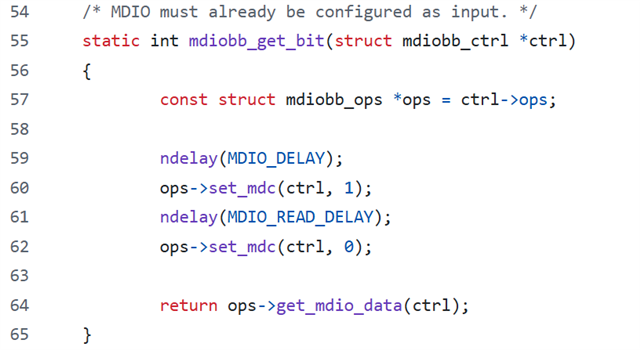

但是、根据 MDIO 的 Linux 驱动程序、读取值似乎根据 MDC 下降沿锁存。

我很困惑、从 MAC 侧(AM64xx)的 MDIO 读取角度来看、哪些信息是正确的。

请您对此发表意见吗?

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好:

我想确认哪些信息是正确的。

*根据数据表,有以下两个规格。

从数据表中、我知道 MAC 侧的 MDIO 读取值基于 MDC 上升沿锁存。

但是、根据 MDIO 的 Linux 驱动程序、读取值似乎根据 MDC 下降沿锁存。

我很困惑、从 MAC 侧(AM64xx)的 MDIO 读取角度来看、哪些信息是正确的。

请您对此发表意见吗?

此致、

尊敬的 Machida Ryuuuichi:

感谢您的提问并耐心等待。

您正在使用哪个 SDK?

您正在使用基于 Linux 或 RTOS 的 SDK 吗?

此致

Ashwani

我们正在使用 Linux SDK。

感谢您的确认。

我正在将您的问题转发给 Linux 以太网专家。

此致

Ashwani

您好、Machida-San、

您使用哪个版本的 Linux SDK?

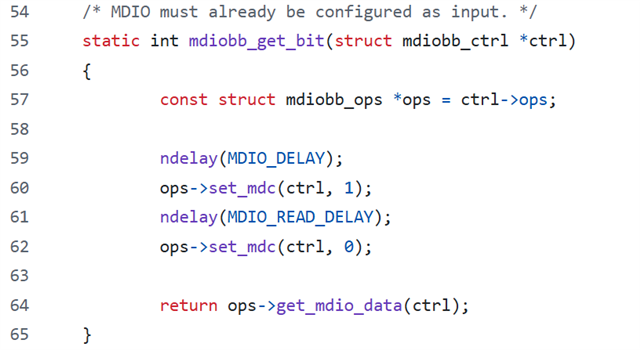

您正在查看的 MDIO 的 Linux 驱动程序看起来是这个驱动程序吗? https://git.ti.com/cgit/ti-linux-kernel/ti-linux-kernel/tree/drivers/net/mdio/mdio-bitbang.c?h=ti-rt-linux-6.6.y#n56

如果是、这似乎是通用的 MDIO Linux 驱动程序、而不是特定于任何 TI 特定的驱动程序。 换句话说、我认为这款 mdio-bitbang.c 驱动程序是在考虑 TI SoC 的情况下设计的。 而对于 CPSW 和 PRU_ICSSG 以太网、我们在此处使用了 davinci_mdio.c 驱动程序 :https://git.ti.com/cgit/ti-linux-kernel/ti-linux-kernel/tree/drivers/net/ethernet/ti/davinci_mdio.c?h=ti-rt-linux-6.6.y。 默认情况下、MDIO 配置为手动模式/位拆裂模式。

快速浏览 davinci_mdio.c 驱动程序时、我看不到它在执行读取时是否专门锁存了下降沿或上升沿的数据。 但是、从 MAC 侧读取 MDIO 的标准可能已在 IEEE 802.3第22条标准中定义。 根据我的理解、MAC 侧的读取操作似乎应该在下降沿锁存、对于 MAC 侧的写入操作、PHY 应该在上升沿读取。 我建议查看 IEEE 802.3第22条标准、看看该标准是否可以消除您的混淆。

root@am64xx-evm:~# dmesg | grep mdio [ 1.776283] davinci_mdio 8000f00.mdio: Configuring MDIO in manual mode [ 1.810321] davinci_mdio 8000f00.mdio: davinci mdio revision 9.7, bus freq 1000000 [ 1.814004] davinci_mdio 8000f00.mdio: phy[0]: device 8000f00.mdio:00, driver TI DP83867 [ 11.679281] davinci_mdio 300b2400.mdio: Configuring MDIO in manual mode [ 11.749426] davinci_mdio 300b2400.mdio: davinci mdio revision 1.7, bus freq 1000000 [ 12.044766] davinci_mdio 300b2400.mdio: phy[15]: device 300b2400.mdio:0f, driver TI DP83869 [ 13.457623] am65-cpsw-nuss 8000000.ethernet eth0: PHY [8000f00.mdio:00] driver [TI DP83867] (irq) [ 13.658217] TI DP83869 300b2400.mdio:0f: attached PHY driver (mii_bus:phy_addr=300b2400.mdio:0f,) [ 13.716410] TI DP83869 mdio_mux-0.0:03: attached PHY driver (mii_bus:phy_addr=mdio_mux-0.0:03, i) root@am64xx-evm:~# uname -a Linux am64xx-evm 6.6.58-rt45-ti-rt-01780-gc79d7ef3a56f-dirty #1 SMP PREEMPT_RT Wed Nov 27 14:15:26 x root@am64xx-evm:~#

如果您有后续问题、敬请告知。

-道林

您好、Daolin-san、

>我建议查看 IEEE 802.3第22条标准、看看它是否能消除您的困惑。

我还查看了 IEEE802.3第22条以了解这一点。

但是、在读写两种情况下、采样时序似乎都被定义为上升沿。

引用 IEEE802.3文档。

读取案例(从 MAC 的角度)

当 MDIO 信号由 PHY 源时、STA 会相对于同步对其进行采样 上升 MDC 边缘。

写入案例(从 MAC 的角度)

当 STA 为 MDIO 信号提供源时、STA 应提供至少10ns 的建立时间和至少10ns 的保持时间(以为基准) 发送到 DOUT 上 MDC

我不知道您为何在下面提到。

从 MAC 侧进行的读取操作似乎应该在下降沿被锁存、对于从 MAC 侧进行的写入操作、PHY 应该在上升沿进行读取。

哪个文档是指的?

此致、

尊敬的 Machida-San:

我不知道您为什么在下面提到。

从 MAC 侧进行的读取操作似乎应该在下降沿被锁存、对于从 MAC 侧进行的写入操作、PHY 应该在上升沿进行读取。

哪个文档是指的?

[/报价]但是在查看实际的 IEEE 802.3文档后、我提到 www.prodigytechno.com/.../mdio-management-data-input-output、我认为此链接中提供的信息可能是对读取 MDIO 操作的错误解释。

仔细观察标准本身:"当 MDIO 信号由 PHY 提供时、STA 会相对于 MDC 的上升沿同步对其进行采样。在 MII 连接器上测量的 PHY 的时钟到输出延迟应至少为0ns、最大为300ns、如图22–19所示"

MDIO/Output 指示"当 PHY 驱动线路时、PHY 必须在时钟上升沿后0ns 至300ns 之间提供 Management_Data_Input 信号。[1] 因此、最小时钟周期为400ns ( 最大时钟速率)、MAC 可在时钟低周期的后半部分安全地对2.5 MHz 进行采样。">en.wikipedia.org/.../"

根据这些信息、我认为这意味着在读取 MDIO 操作期间、MAC 采样的 MDIO 应在时钟的上升沿完成。

[/quote]如果是、这似乎是通用的 MDIO Linux 驱动程序、而不是特定于任何 TI 特定的驱动程序。 换句话说、我认为这款 mdio-bitbang.c 驱动程序是在考虑 TI SoC 的情况下设计的。 而对于 CPSW 和 PRU_ICSSG 以太网、我们在此处使用了 davinci_mdio.c 驱动程序 :https://git.ti.com/cgit/ti-linux-kernel/ti-linux-kernel/tree/drivers/net/ethernet/ti/davinci_mdio.c?h=ti-rt-linux-6.6.y。 默认情况下、MDIO 配置为手动模式/位拆裂模式。

快速浏览 davinci_mdio.c 驱动程序时、我看不到它在执行读取时是否专门锁存了下降沿或上升沿的数据。

[/报价]我无法对您似乎引用的 mdio-bitbang.c 驱动程序进行注释。 我只能说、AM64x SoC 使用 davinci_mdio.c 驱动程序进行 MDIO 操作。 MDIO 是否存在特定的功能问题? 您正在使用什么 Linux SDK?

-道林