工具/软件:

亲爱的 champ、

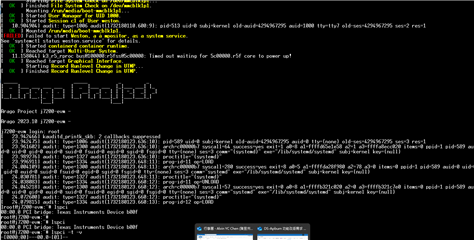

客户正在使用 J7200 EVM、并尝试使用 J7200 EVM PCIe 插槽上的 PCIe 卡来验证 PCI 功能。

SDK 9.0和 SDK 10.0均按照以下说明进行尝试

使用所需的标志重建 Linux 内核、并使用两个 PCIe 插槽上安装的 PCIe 以太网卡启动 EVM。

Linux 驱动程序配置

必须启用以下配置选项才能将 PCI 控制器配置为在根复合体模式下使用。

CONFIG_SOCIONEXT_SYNQUACER_PREITS=y CONFIG_PCI=y CONFIG_PCI_MSI=y

CONFIG_PCI_J721E=y CONFIG_PCIE_Cadence=y CONFIG_PCIE_Cadence=y

CONFIG_PCIE_CADDENCE HOST_HOST=y

但是、lspci 无法获取任何器件 ID、只能获取 RC pid vid。

是否需要进行任何其他修改?

我们如何使用 SDK 10.1预编译映像来验证它? 说明会有所帮助。

Br、Rich