主题:SysConfig 中讨论的其他器件

工具/软件:

尊敬的专家:

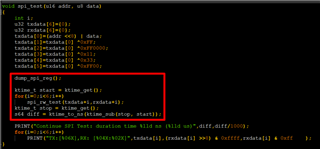

我使用以下简单的程序片段来说明我们的需求。

我们希望尽可能缩短读写时间。

我们的中断程序每125us 执行一次。 每次进入时、

需要执行6次 SPI 读取和写入两次。

以下是模拟一个周期所需的时间。

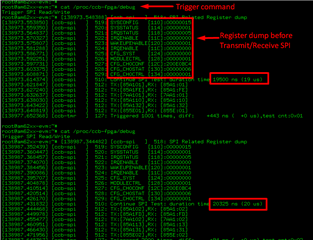

下面显示了每次执行工作之前相关寄存器的转储以及所消耗时间的计算。

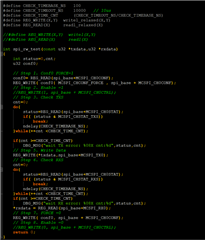

以下是用于读取和写入 SPI 的程序。

示波器上显示的时间使用 writel/readl。

之后、使用 writel_relaxed/readl_relaxed 可以缩短一段时间、例如控制台上显示的时间。

以下是控制台中显示的执行结果

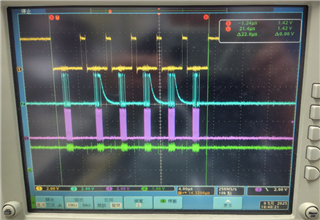

以下是示波器显示的结果。 (时钟= 25MHz、数据= 24位)

我们猜测、如果不能通过软件将 CS 的控制写入强制位、则可能会缩短一段时间。

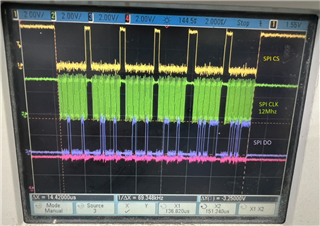

以下是我们现有 Cavium 平台上的测试结果。(clock=Cavium 12MHz、data=24位)

我们可以看到、区别在于没有冗余 CS。

我不确定从 CH0STAT 等待 TXS/RX 是否远大于实际传输延迟。

谢谢

Daniel