主题中讨论的其他器件:AM620-Q1、

工具/软件:

您好、团队

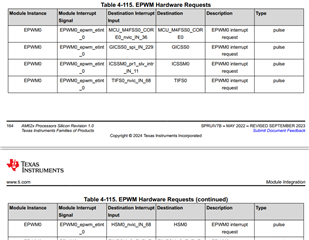

请为 AM620-Q1中的 ECAP、WDT、EQEP 外设添加软件支持、以适用于 M4F 内核

背景:

CCS v12.8.1

MCU + SDK AM62x_10_01_00_33

我们使用 M4F 内核进行 BLDC 电机控制(A53内核无法满足实时要求)。 控制过程使用三个驱动器:ECAP、WDT 和 EQEP。

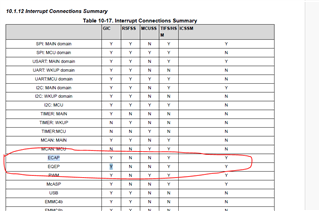

由于 TRM 规定外设寄存器可以跨域运行、因此我们相应地设计了硬件。

但是、在开发过程中、

我们发现、当前 SDK 只能将上述三个外设分配给 A53内核、而不能分配给 M4F 内核。

这要求 TI 在软件级别修改 SDK 或 syscfg (资源分配工具)。