主题:SysConfig 中讨论的其他器件

工具/软件:

尊敬的专家:

我正在使用 SDK RTOS 10.1为 J784S4 EVM 构建 FreeRTOS 应用。

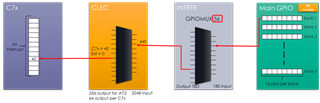

我尝试将中断从主 GPIO0存储体0 (引脚11)路由到 C7x 内核1。

电路板处于"无引导模式"、我将应用程序加载到 c7x 内核1上。

我已正确初始化焊盘配置和 GPIO。 按下 SW3按钮后可以读取 GPIO0_11的值。

我已经 使用 SysConfig 修改 sciclient_defaultBoardcfg_rm.c 并设置中断。

但我无法到达 回调函数。

这是我对中断路径的理解:

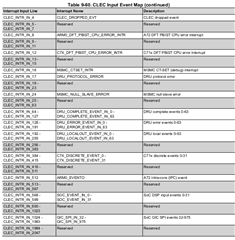

145 = GPIOMUX_INTRTR0_IN_145 (=来自 GPIO0组0的 INTRTR0输入)

44 = COMPUTE_CLUSTER0_CLEC (=向 CLEC 输出 INTRTR)

56 = SCIServer 为主机 C7x_0_1设置 GPIOMUX_INTRTR0控制寄存器56

440 = COMPUTE_CLUSTER0_CLEC_SOC_EVENTS_IN_440 (=来自 GPIOMUX_INTRTR0 56的 CLEC 输入)

40 = GPIO 示例中使用的 C7x 中断号

我使用了"J784S4_TLO.20150116.xlsx" Register_Public_来获取以下寄存器地址:

- GPIOMUX_INTRTR0

- GPIO0

- COMPUTE_CLESTER0_CLEC

使用 CCS 存储器浏览器视图、我检查了每个寄存器、它们看起来都是正确的。

0xa000e4 = 0x10091

0x600008 = 0x1

0x600010 = 0xFFFFFFFF

0x600034 = 0x0

0x79b81000 = 0x411000028

我可以通过写入 CLEC 发送寄存器来触发中断(代码到达回调函数)。

按下 SW3按钮后、可以在 组中断状态寄存器中看到该标志。

我试过 :

- 编译的软件包文件。

- 使用 OSAL、然后使用 CSL 层+对寄存器进行写入。

- 使用 不同的 引脚、组、然后使用 wkup GPIO 模块。

我找到这篇帖子、与我的问题非常接近、但没有答案: J784S4XEVM:C7x GPIO 中断问题-处理器论坛-处理器- TI E2E 支持论坛

感谢你的帮助

Charles