主题中讨论的其他器件:AM62A7、 SysConfig

工具/软件:

您好:

我们使用 OSPI 控制器将出现此问题的 IP 移植到具有 FPGA 的 AM62A7平台。 我们将 OSPI 控制器交换到了 GPMC 控制器。 使用 DMA 使用此接口进行测试、结果没有损坏数据。 因此、这个 DMA 问题似乎仅出现在 OSPI 控制器上。

谢谢、

Victor

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好:

我们使用 OSPI 控制器将出现此问题的 IP 移植到具有 FPGA 的 AM62A7平台。 我们将 OSPI 控制器交换到了 GPMC 控制器。 使用 DMA 使用此接口进行测试、结果没有损坏数据。 因此、这个 DMA 问题似乎仅出现在 OSPI 控制器上。

谢谢、

Victor

Victor

您是否有关于失败的更多详细信息(我知道您链接到的上一篇文章中有一些详细信息)。 这是否仍然是同样的失败?

DMA 中显示的错误有一种模式。 第一个数据缓冲区始终没有错误。 第二到第五个数据缓冲区始终有32位错误。 第二个数据缓冲区中的错误始终从第18个字节开始、第三个数据缓冲区中的错误从第22个字节开始、第四个数据缓冲区中的错误从第26个字节开始、第五个数据缓冲区中的错误从第30个字节开始。 则第六到第九个数据缓冲区没有错误。 该循环在第十个缓冲区上重复、但起始偏移可能会发生变化。

后续重新启动测试将始终遵循这种错误数据缓冲区和偏移的模式、但损坏的数据绝不会相同、而是遵循类似的模式。

故障是否看起来是软件功能错误、容易且一致地重现等? 如果时序不同、您是否会看到任何区别(例如、如果您以较低的速度运行 OSPI)? 我假设没有简单的方法可以在 TI EVM 上显示再现性?

是的、这是同样的失败。 我们首先注意到了集成到 FPGA 的 AM64EVM。 我们现在看到它在我们的 AM62A7电路板上、在 ASIC 上具有相同的 IP。

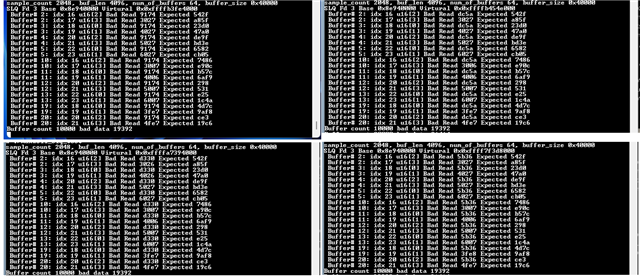

我运行了4个测试、其中前20个故障的状态将发送到控制台端口。 我插入了以下4项测试的屏幕截图。 请注意这些故障的相似之处。 在4个测试中、缓冲区和缓冲区中的索引都相同。 请注意每个迭代中以及在4个测试中的坏读取数据模式。

我不再认为这是一个缓存问题、因为该 OSPI 驱动程序与我编写的另外两个 DMA 驱动程序共享用于分配目标缓冲区的通用代码、这两个驱动程序目前在我们的系统中工作正常。 一个驱动器在 DMA 循环模式下使用 SPI、另一个驱动器使用 GPMC 作为软件触发的 DMA 传输。 我认为故障出现在./drivers/dma/ti /*文件之一中。

您可以使用其中一个 EVM 和 QSPI 闪存复制此内容。 您需要将已知的4K 字节模式写入 QSPI 闪存、并以10ms 的速率重复读取。

与其他 DMA 驱动程序不同、如果该 OSPI 驱动程序是 PKTDMA 或 BCDMA、则它没有在器件树中指定。 在驱动程序中、也没有调用 dmaengine_slave_config ()。 我假设所有这些都在为该 OSPI 控制器设置 DMA 的./drivers/dma/ti /*目录中处理、很可能是该代码中的错误。

我想分享更多测试结果。

如上一篇相关文章中所述、驱动程序可以通过 DMA 或 CPU 从 OSPI 控制器读入数据。 使用 DMA 时、数据帧将为4K 字节、以最大限度地减少中断次数。 使用 CPU、由于 FIFO 的大小、数据帧将为512字节。 使用 CPU 时、出现错误数据问题。 如果我们将 DMA 配置为也使用512字节的数据帧、则 ASIC 中的 IP 在由 DMA 或 CPU 驱动的传输之间不会看到任何差异。 因此、我使用 DMA 进行了一项测试、使用512字节的数据帧来传输数据、而前一篇文章中使用的是4K 字节。 以下是4项测试的结果。 请注意、不良数据与512数据帧在4个测试中的相似性、以及与前一篇文章中的结果的相似性。 根据这两个测试结果、相同的缓冲区和索引上会发生错误。

请注意、在使用512或4K 数据帧的两个 DMA 传输中、某些缓冲区的不良数据为零、而其他缓冲区的数据为2个错误数据。 每个缓冲区之间的区别在于数据帧中发送到 ASIC IP 的读取地址。 读取地址从0开始、每个连续的缓冲区将读取地址递增(数据帧大小- 4)、然后在0x10000处回滚。

由于读取地址为0的第一个缓冲区一直没有失败、因此我决定将读取地址修改为从不递增。 因此、所有数据帧的读取地址都为0。 我修改了测试程序、以便在每次数据传输后重置并重新启动 ASIC 中的 IP。 无论512或4K 数据帧如何、修改后的测试都不会导致错误数据。

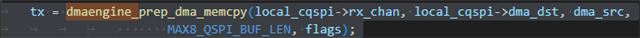

读取地址在以下代码中通过 参数 DMA_src 传递到 DMA。 是否知道读取地址导致一些缓冲区失败的原因?

谢谢、

Victor

读取地址从0开始、每个连续的缓冲区将读取地址递增(数据帧大小- 4)、然后回滚到0x10000。 [/报价]这是您的代码正在执行的操作还是您观察到发生的情况?

如果是前者、为什么以增量"-4"? 在上一次 DMA 传输中是否读取了最后4个字节并将在下一次 DMA 传输中再次读取? src 和 DST 地址是否都按"DATA FRAME SIZE - 4"递增?

在 drivers/spi/spi-cadence-quadspi.c 中的函数 cqspi_direct_read_execute ()的开头、它会检查 cqspi_use_phy ()是否存在。 您的用例是否使用 OSPI PHY 模式?

我找到了问题、并使用了一种解决方法。 问题出在下面所示的函数调用中 dma_src。 此参数用作在 QSPI 数据帧中传递的基地址。 数据帧的大小为4096个字节、其中第一个字节是操作码、后跟3个字节(包含基地址)、最后是4092个字节的数据。 此 DMA_src 从0开始、每个连续的数据帧递增4092、直到超过0x10000、然后模数为0x10000。

如果我将 DMA_src 更改为递增4096、从而使数据帧的大小为5000字节、则损坏的数据会消失。 这会导致该大小出现问题、因为我认为每次 DMA 传输都需要目标缓冲区为4K 字节对齐。 为了解决此对齐问题、每个5000字节数据帧都存储在环形缓冲区中、每个缓冲区从8192字节的偏移量开始。

我不理解的是为什么这个 bug 发生。 如果我的 IP 存在未对齐基地址的问题、它发回的第一个字节应该有问题。 但在某些数据帧中、它始终是位于特定位置的四个字节。 不管怎么说,也许你可以解释为什么这个 bug 发生。

您好、Victor、

感谢您在调试方面取得的巨大进展。

DMA 本身没有缓冲区地址对齐要求。 数据缓冲区可以位于任何字节地址、DMA 硬件本身负责传输对齐。

我想知道问题是否出在 OSPI 接口而不是 DMA 上。

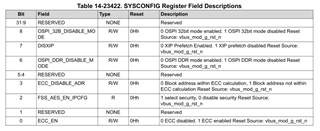

这是 OSPI SysConfig 寄存器:

其位7"DISXIP"默认为0、这表示启用了 XIP 预取。 您能否在您的电路板上检查该位是否仍然为0? 如果是、请手动将其设置为1以禁用预取、以查看它是否会影响此数据损坏问题。

您好:

我将这段代码添加到 cqspi_controller_init ()中、并更改代码以确保在获得损坏的数据时 dma_src 不再像以前那样对齐。 测试导致相同的故障、这意味着此更改没有执行任何操作。

谢谢、

Victor