工具/软件:

尊敬的专家:

启用 DRAM 内联 ECC 后、R5 u-boot 将提前初始写入 ECC 保护区域。

这将增加系统引导延迟(即使使用 BIST 模块初始写入)并且对用户体验不友好。

为了减少引导延迟、我建议将 ECC 保护区域的初始写入行为从 R5 u-boot 阶段推迟到引导后阶段(例如、在 Linux 启动后)

在给定针对 ECC 受保护区域的 SoC RMW (读取-修改-写入)策略的情况下、这意味着、

- 系统启动后、如果我初始将特定的 PATTEN 写入 ECC 保护区域(未在 R5 u-boot 中初始写入、以减少引导延迟)

- 由于 RMW、在写入操作之前将有读取操作、并且这种额外的读取操作将获得垃圾数据并生成 ECC 错误中断。

我的权变措施解决方案是、 在系统启动后、在初始写 ECC 保护区域之前禁用 ECC 中断、然后在初始写操作后恢复 ECC 中断。

然后、我在 SDK 中执行以下实验 TI-PROCESSOR-SDK-LINUX-ADAS-j721e-EVM-10_01_00_04

在 R5 u-boot 阶段、

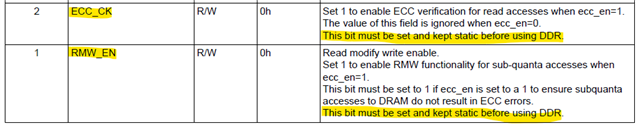

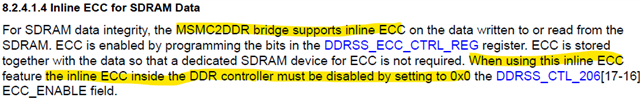

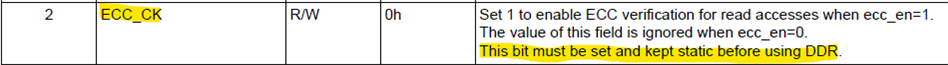

- 例程 TI、ECC-ENABLE ="true" 和 ss_cfg 寄存器范围 目标 k3-j721e-ddr.dtsi 才能启用 MSMC2DDR 桥中的内联 ECC 功能

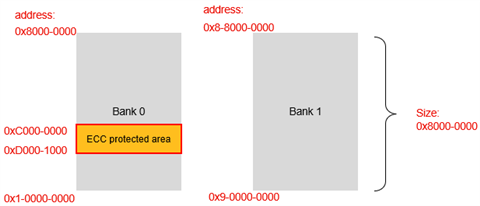

- 配置 ECC 保护区0xC000-0000 ~ 0xD000-1000

- 然后、 使用特定 PATTEN 0x12345678死区的初始写入 DRAM 区域0xC000-0000 ~ 0xD000-0000

- 也就是说、0xD000-0000 ~ 0xD000-1000受 ECC 保护、但不会初始写入。

在 A72 u-boot 阶段、

| => MD.l 0xC0000000 0x4 // 0xC000-0000 ~ 0xD000-0000已被初始写入 c0000000:死牛肉12345678死牛肉12345678...xV4… XV4。 |

| => MD.l 0x029800a8 0x1 // DDRSS_V2A_INT_SET_REG、查找启用的 ECC 中断 029800a8:00000038 // 0x38表示启用了多个1位/1位/2位错误中断 => mw.l 0x029800ac 0x38 0x1 // DDRSS_V2A_INT_CLR_REG、写入0x38以禁用 ECC 中断 => MD.l 0x029800a8 0x1 // DDRSS_V2A_INT_SET_REG、现在 ECC 中断被禁用 029800a8:00000000 |

|

=> mw.l 0xd0000000 0x12345678 0x1000 //尝试初始写入 ECC 保护区0xD000-0000 ~ 0xD000-1000 x0:0000000000000faf x1:00000000d0000144 代码:d2800001 94029cfd 93407e82 aa1303e1 (d1000400) 正在重置... |

下面是我的问题:

- 禁用 ECC 中断时、为什么初始写入会导致异常? 如何避免或处理此类异常?

- 有任何问题吗 的 ECC 错误处理示例代码 MSMC2DDR 桥接器 ?

顺便说一下、我已经在 ti-processor-sdk-rtos-j721e-evm-10_01_00_04/sdl/examples/ecc 中找到了 ECC 错误处理示例代码

但它利用 DDRSS 中的 ECC 实现、而不遵循 SDK 文档中的建议

将为 MSMC2DDR brige 提供 ECC 错误句柄示例代码:-)

我期待您的反馈。

谢谢。