工具/软件:

您好专家!

对于使用 DP83826 PHY 的基于 AM4376的设计、我们在以太网链路稳定性方面存在一个奇怪的问题。

我们有一个基本上是 AM4376的设计、它具有两个以太网端口、通过 MII 连接在 DP83826上实现。

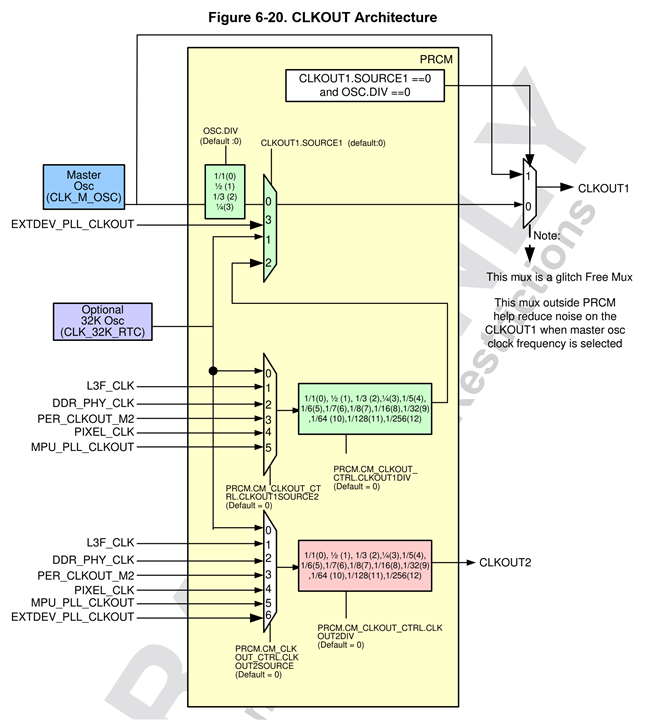

端口1 PHY 由 AM4376 CLKOUT1信号计时、端口2 PHY 由 AM4376 CLKOUT2信号计时。

AM4376输入时钟是一个具有+/-50ppm 的25MHz 振荡器。

链路有时会丢失(~每10秒到每小时)。

仅当两个设备使用每个设备的端口2直接连接、但不涉及端口1时、才会出现此问题:

连接到设备2端口1的设备1端口1正常

连接到设备#2端口1的设备#1端口2正常

连接到设备#2端口2的设备#1端口1正常

连接到设备#2端口#2的设备#1端口2不正常

带有"自身"的链路(将 PHY 端口2 RX 连接到端口2 TX)也很稳定:

连接到设备1端口2的设备1端口2正常

我调查了 PHY 寄存器、发现端口2上的寄存器0x14 (虚假载波计数器)和寄存器0x15 (接收错误计数器)正在递增。

在某些时候、有足够的错误会触发 PHY 的" RX 上的快速链路断开"功能。

链路中断后、会自动再次建立链路。 结果是100M 全双工。

通过 MDIO 进行的搭接和配置与两个 PHY 相同、因此我研究了两个端口的差异、并尝试通过 CLKOUT1引脚为两个 PHY 计时。

这消除了所有错误、链路稳定、无错误寄存器计数。

因此、问题似乎与"CLKOUT2"相关。

n´t 使用 CLKOUT2计时的 PHY 自身具有稳定的链路(TX 连接到 RX)、因此它看起来不像时钟中断或类似的中断。

我假设是 CLKOUT2上的频率容差/抖动。 有时、两个 CLKOUT2增加的容差/抖动太大而无法保持链路。

CLKOUT2由 AM4376内部低抖动 PLL (EXTDEV_PLL)控制。

设置:

CLKINP:25MHz (主 osc 时钟输入)

分隔符 N:9

乘数 M:200

后分频器 M2:10

SD_DIV:2.

CLKOUT2分频器:2.

因此、PLL 应锁定在500MHz (25MHz /(9+1)* 200、PLL 输出为50MHz (500MHz / 10)、在 CLKOUT2分频器中除以2、为 CLKOUT2提供25MHz。

SSC 已停用。

EXTDEV_PLL 配置的寄存器内容:

[0x44DF2E60]= 0x7

[0x44DF2E64]= 0x1

[0x44DF2E6C]= 0x200c809

[0x44DF2E70]= 0x38a

[0x44DF2E84]= 0x80000

[0x44DF2E88]= 0x0

[0x44DF2E8C]= 0x0

我´m 想知道这一点、因为在参考手册中明确指出、CLKOUT2可用于为外部 PHY 计时。

问题:

您过去看到过类似这样的东西吗? CLKOUT2频率精度是否存在已知问题? 还是 DP83826对 CLK 容差的特殊敏感度?

您可以查看 PLL 设置吗? 是否有需要优化的地方(例如、PLL 锁定频率较高/较低、尝试旁路模式…)?

谢谢!

基督教