工具/软件:

尊敬的专家:

你好。

根据 AM335X 的技术手册:

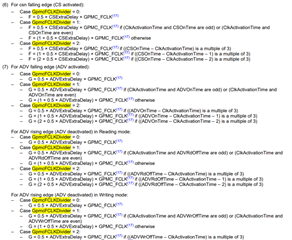

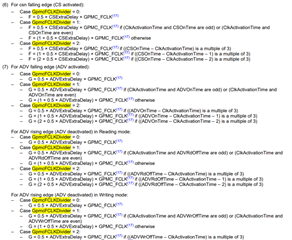

p128仅指示 GpmcFCLKDivider 的情况0、1和2:

问:如果是3个、会发生什么情况? 任何方程?

谢谢你。

此致、

阿奇·A·

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的专家:

你好。

根据 AM335X 的技术手册:

p128仅指示 GpmcFCLKDivider 的情况0、1和2:

问:如果是3个、会发生什么情况? 任何方程?

谢谢你。

此致、

阿奇·A·

尊敬的 Archie:

不知道为什么他们没有将文档扩展到4分频。 GPMCFCLKDIVIDER 确实有4分频选项(0x3)。

我可以提出的唯一原因是、ClkActivationTime 在 START 访问时间后仅支持多达2个 GPMC_FCLK 周期、因此4分频模式比其他模式具有更严格的限制。

您所附的注释也不涉及 TimeParaGranularty 的使用、但我认为这会使 OnTime/OffTime 计数器的延迟加倍。

尝试强制执行的注释是将控制信号转换与分频时钟的上升沿对齐。 GPMC 不会强制您执行此操作-信号在相应 OnTime/OffTime 位字段中编程的任何 FCLK 周期上进行转换。

GpmcFCLKDivider

对 GPMC_FCLK 时钟进行分频

0x0:GPMC_CLK 频率= GPMC_FCLK 频率

0x1:GPMC_CLK 频率= GPMC_FCLK 频率/2

0x2:GPMC_CLK 频率= GPMC_FCLK 频率/3

0x3:GPMC_CLK 频率= GPMC_FCLK 频率/4

ClkActivationTime

输出 GPMC_CLK 激活时间

0x0:在开始访问时间 GPMC_CLK 的第一个上升沿

0x1:GPMC_CLK 的第一个上升沿、在 START 访问时间后一个 GPMC_FCLK 周期

0x2:GPMC_CLK 的第一个上升沿、在 START 访问时间后的两个 GPMC_FCLK 周期

0x3:保留

此致、

标记