工具/软件:

尊敬的专家:

我们有2个 TDM 流连接到两个 McASP 接口、每个流具有32个 Tx 和32个 Rx 时隙、每个时隙为8位(A 或 Mu 定律)、

工作模式为从模式、因此 FPGA/CLK 是输入(来自 FS)、有64个发送通道和64个接收通道要处理。

在 McASP 接口中、我们希望将其设计为乒乓模式、如下所示:

- 每个 TX 和 RX 时隙都有一个独立的连续存储空间

2.每个缓冲区空间可以存储20ms 的数据(160字节),每10ms 处理一次数据(80字节)

3、这些数据可以通过 DMA 自动移动到相应的区域

4、应用层软件可以根据需求每隔10ms 写入或读取一次指定的通道数据

我们的问题是:

1、上述设计要求是否可行? 是否存在任何已知瓶颈、如 DMA 数量、空间或时间限制等

2、是否有比上述更好或更快的设计?

3.是否有类似的参考示例? (DTS、驱动程序、DMA 控制...)

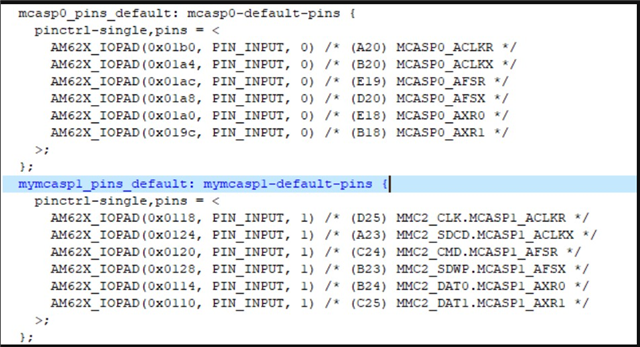

硬件信息如下:

McASP0_ACLKR = McASP0_ACLKX = McASP1_ACLKR = McASP1_ACLKX <= FPGA CLK = 2MHz

McASP0_AFSR=McASP0_AFSX=McASP1_AFSR=McASP1_AFSX <= FPGA FS = 8kHz

McASP0_AXR0 =>FPGA 流0 RX

McASP0_AXR1 <= FPGA 流0 TX

McASP1_AXR0 => FPGA 流1 RX

McASP1_AXR1 <= FPGA 流1 TX

TDM 流:

FS:8K

CLK:2MHz

谢谢

Daniel