主题中讨论的其他器件:SK-AM62

工具/软件:

在 eMMC 部分的原理图检查清单中:

7.2.2.1.1.3信号端接

提供以下端接:

•为 MMC0_CLK 信号连接串联电阻(0 Ω、靠近处理器)、为连接外部下拉电阻

MMC0_CLK 信号(靠近 eMMC 器件)。

•为数据线(MMC0_DAT0)连接外部上拉电阻(靠近 eMMC 器件)。 eMMC 器件(如

只要 eMMC 器件符合 eMMC 标准、就为数据信号启用了上拉电阻

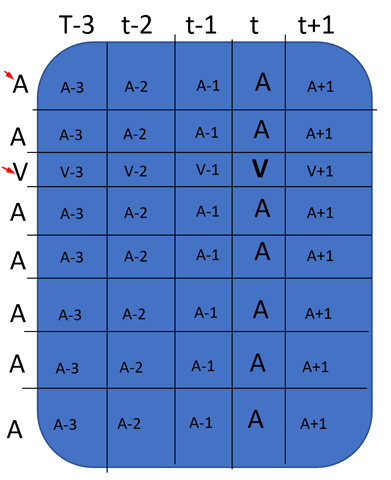

默认为 MMC0_DAT1..7。 进入4位模式时、eMMC 器件会关断其 MMC0_DAT1..3上拉电阻

进入8位模式时、MMC0_DAT1..7上拉电阻。 eMMC 主机软件应打开相应的电源

DAT 在更改模式时拉取。

#1。 0 Ω 电阻器用于 MMC0_CLK 的用途是什么?

#2. 在更改模式时、软件打开 DAT 上拉电阻、DAT 引脚上是否必须上拉电阻? 如果是、为什么 eMMC 器件在开关期间将其从打开状态关闭?

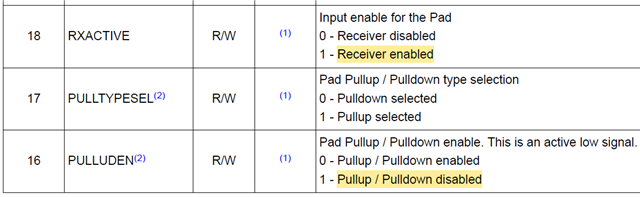

#3. 是否在 SDK 中实现了在更改模式时打开 DAT 上拉电阻? 未在驱动程序 sdhci_am654.c 中找到 padconfig 信息