主题中讨论的其他器件:AM62L

工具/软件:

尊敬的专家:

代表我的客户发布:

我们准备了一些带有 AM62L USB 和 UART 的定制电路板、并希望使用 USB-DFU 加载引导加载程序二进制文件。

借助 TI EVM、我可以轻松引导至 uboot、但在我们的电路板上、我在 BL1之后的控制台上看不到任何消息(tiboot3.bin)。

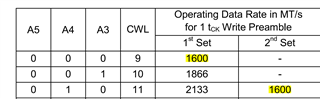

我们 SoM 和 TI EVM 的二进制文件 tiboot3.bin 和 tispl.bin 具有相同的 DDR 设置和 DDR 大小、但 UART 和 USB 弹出的所有内容都相同。

但让我分享 consol 日志:

NOTICE: bl1_plat_arch_setup arch setup NOTICE: Booting Trusted Firmware NOTICE: BL1: v2.12.0(release):11.00.09-7-g144a586a83d2-dirty NOTICE: BL1: Built : 14:40:34, May 5 2025 INFO: BL1: RAM 0x7080b000 - 0x7080f000 INFO: lpddr4_init <-- INFO: lpddr4 dtb: ctl-data ptr=0x7080718c, pi-data=0x70807834, phy-data=0x70807da4 NOTICE: BL1: dram_class: 10 INFO: memory node =0x28 INFO: lpddr4: probe done INFO: lpddr4/ddr4: init done INFO: start-status: offset =0x0 INFO: start-status reg: before =0x10460a00 A. INFO: Doing normal DDR initINFO: lpddr4: Start DDR controller INFO: lpddr4: start completed successfully status=0x0 INFO: start-status reg: after =0x10460a01 INFO: LPDDR4 start completed !! NOTICE: lpddr4: post start - PI training status=0x29c02000 INFO: lpddr4: post start - CTL Interrupt status=0x4 INFO: start-status reg: after =0x10460a01 INFO: LPDDR4 start completed !! NOTICE: bl1_platform_setup DDR init done NOTICE: k3_bl1_handoff ENTERING WFI - end of bl1

与该 EVM 相比、结果是:

对于我们的电路板:

注意:LPDDR4:POST START - PI 训练状态=0x29c02000

INFO:LPDDR4:POST START - CTL Interrupt STATUS=0x4

在 EVM 上:

注意:LPDDR4:POST START - PI 训练状态=0x27c0a000

信息:LPDDR4:启动后- CTL 中断 STATUS=0x0

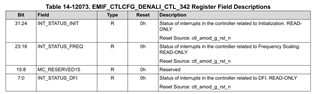

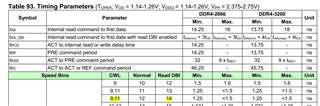

遗憾的是、TRM 中未描述两个 INT_STATUS 寄存器的内容。 您能否找出这是否表示 RAM 出现故障? DDR 控制器是否提供更详细的寄存器说明?

谢谢您、

Marinus