主题中讨论的其他器件:AM62L、 SysConfig

工具/软件:

尊敬的支持:

您是否可以查看以下分配的焦点客户问题:

在 DDR 布局指南中、我们有以下内容:

您能否证实这不适用于 我们、因为我们使用的是 LPDDR4、而不是 DDR4?

如果我们使用 DDR4、AM62Lx 中的控制器/PHY 是否甚至支持 CRC?

我认为本文档是通用的、因此涵盖了许多其他器件的场景/功能、这可能不适用于 我们的案例;您能否确认?

谢谢!

Blake

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的支持:

您是否可以查看以下分配的焦点客户问题:

在 DDR 布局指南中、我们有以下内容:

您能否证实这不适用于 我们、因为我们使用的是 LPDDR4、而不是 DDR4?

如果我们使用 DDR4、AM62Lx 中的控制器/PHY 是否甚至支持 CRC?

我认为本文档是通用的、因此涵盖了许多其他器件的场景/功能、这可能不适用于 我们的案例;您能否确认?

谢谢!

Blake

您好 Blake、

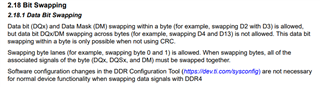

感谢您的澄清。 有这些指南的更新版本从该屏幕截图我认为,虽然它几乎说相同的事情:

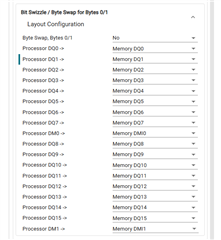

至于字节交换和位混合限制、这对于 LPDDR4应该是准确的。 配置 SysConfig 工具是无错误的理想方法、屏幕截图如下所示:

它将确保不违反位交换/重排逻辑(下拉菜单项会进行调整)。

关于 CRC、IP 应与符合 JEDEC 标准的 DDR4存储器搭配使用、这些存储器支持 ALERT_n 引脚上的 CRC 错误、不过如果控制器需要明确启用该功能、这一问题会有点模糊。

此致、

Lucas

您好、Lucas:

糟糕! 看起来像一个拼写错误打倒了我们:

我的问题似乎不清楚、这是因为我原始电子邮件中存在拼写错误。

我在第一封电子邮件中发布的片段来自 DDR 设计指南、位于下 DDR4 部分。

我们 没有使用 DDR4 。 不同应用 LPDDR4 。

在 LPDDR4部分中、没有提到无法使用 CRC 保持一致。

所以、我的问题是:是 CRC 使用时支持 LPDDR4 ?

如果是、那么在我们无法使用的情况下、同样的注释也适用 CRC 符号、该协议会很有用 LPDDR4 ?

根据数据表和参考手册、我可以看出、LPDDR4没有 CRC、但有内联 ECC。

道歉-应该有健全检查它更好。

有一个很棒的周末!

Blake

您好 Blake、

不用担心! CRC 不除了 JEDEC LPDDR4规范、因此 它在 LPDDR4或控制器中没有标准硬件支持。 如果您想对存储在 DRAM 中的数据进行 CRC 检查、它将位于更高级别的软件抽象层中。 从 ARM 内核的角度来看、位混合/字节交换是不可见的(全部都在 DDR IP 本身中处理)。

您对存在内联 ECC 是正确的、这是硬件管理的 ECC、主要将 ECC 代码存储在 DRAM 内(因此与数据并排存储)、并使用这些代码进行单错校正+双错检测(SECDED)。 这减少了可用的 DRAM 数量、但允许硬件进行错误检查。

还有一个很棒的周末!

此致、

Lucas