工具/软件:

尊敬的 TI 支持团队:

我们使用 SDK 10。

我正在开发 J721E (TDA4VM)、需要在26 MHz 上运行 UFS 控制器的 MCLK。

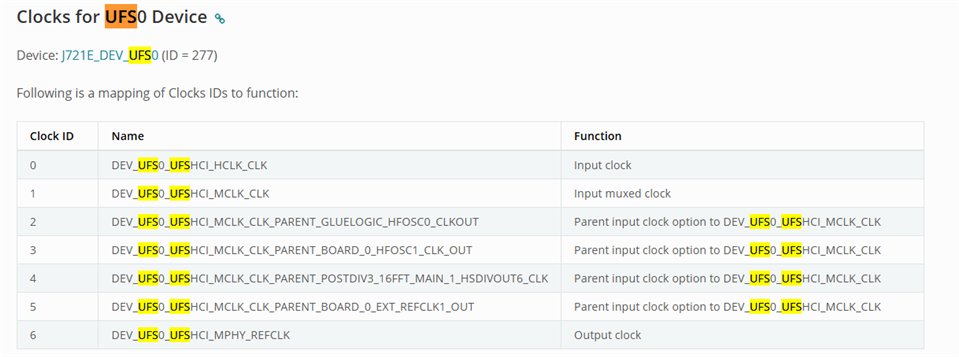

使用、 k3conf 我可以看到相关的时钟 ID:

root@j721e-evm:~# k3conf dump clock 277.

------------------------------------------------------------------------------------ |

| VERSION INFO |

------------------------------------------------------------------------------------ |

| K3CONF |(版本0.3-nogit Builded Thu Jul 25 14:13:02 UTC 2024)|

| SoC | J721E SR1.1 |

| SYSFW | ABI:4.0 (固件版本0x000a '10.0.8--v10.00.08 (Fiery Fox))|

------------------------------------------------------------------------------------ |

|-------------------------------------------------------------------------------------------------------------------------------- |

|器件 ID |时钟 ID |时钟名称|状态|时钟频率|

|-------------------------------------------------------------------------------------------------------------------------------- |

| 277 | 0 | DEV_UFS0_UFSHCI_HCLK_CLK | CLK_STATE_READY | 250000000 |

| 277 | 1 | DEV_UFS0_UFSHCI_MCLK_CLK | CLK_STATE_READY | 19200000 |

| 277 | 2 | DEV_UFS0_UFSHCI_MCLK_CLK_PARALY_GLUELOGIC_HFOSC0_CLKOUT | CLK_STATE_READY | 19200000 |

| 277 | 3 | DEV_UFS0_UFSHCI_MCLK_CLK_PARALT_Board_0_HFOSC1_CLK_OUT | CLK_STATE_READY | 0 |

| 277 | 4 | DEV_UFS0_UFSHCI_MCLK_CLK_PARALT_POSTDIV3_16FFT_MAIN_1_HSDIVOUT6_CLK | CLK_STATE_READY | 19200000 |

| 277 | 5 | DEV_UFS0_UFSHCI_MCLK_CLK_PARALT_Board_0_EXT_REFCLK1_OUT | CLK_STATE_READY | 0 |

| 277 | 6 | DEV_UFS0_UFSHCI_MPHY_REFCLK | CLK_STATE_READY | 0 |

|-------------------------------------------------------------------------------------------------------------------------------- |

目标

•使 ID 1 (MCLK)使用26 MHz 处的父 ID 3 (HFOSC1/EXT_REFCLK1)。