请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DRA829J 工具/软件:

尊敬的 TI-Team、

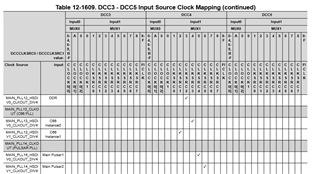

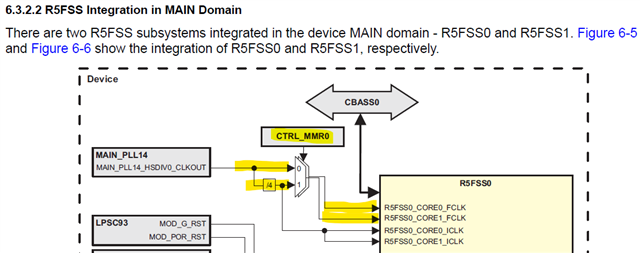

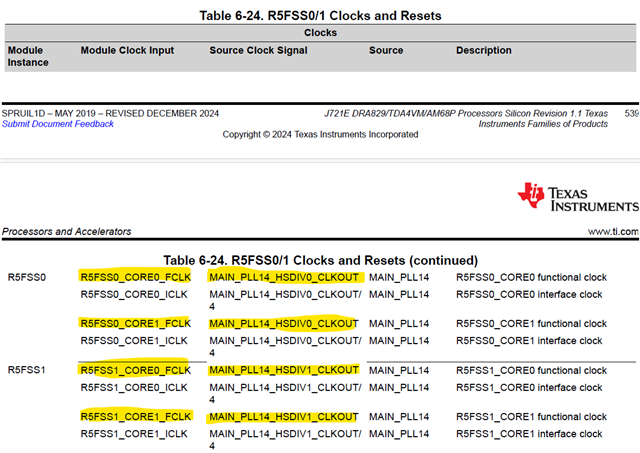

在检查 TRM 的 R5FSS0和 R5FSS1功能时钟源时、我们意识到在集成图中、有一个 CTRL_MMR0寄存器用于选择时钟源。

但是、使用相应的选项检查表时、只有一个值。 此外、我们没有找到任何用于为 R5FSS0和 R5FSS1选择时钟源的寄存器。

图表错误或表需要更新。 请参阅以下图片:

您能否检查并确认哪一项信息正确?

提前感谢您。

此致、

António μ s