工具/软件:

尊敬的专家:

SDK10、U-Boot 2024.04。

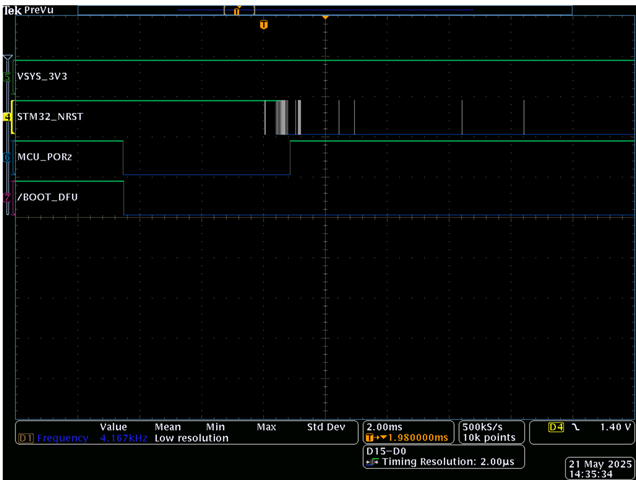

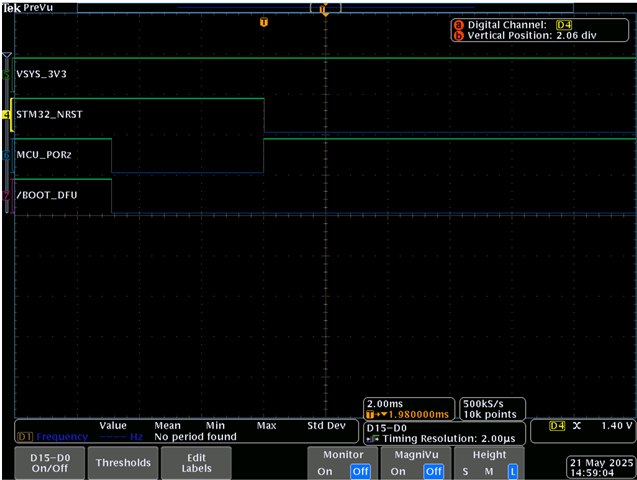

我们有一个定制电路板、外部 STM32处理器用作 RESET CPU。 这个外部 CPU

负责复位 SoC 或将引导配置设置为 USB (DFU)模式。 STM32

设置相应的引导加载程序、然后切换 MCU_PORz (将其驱动为低电平、然后驱动为高电平)。

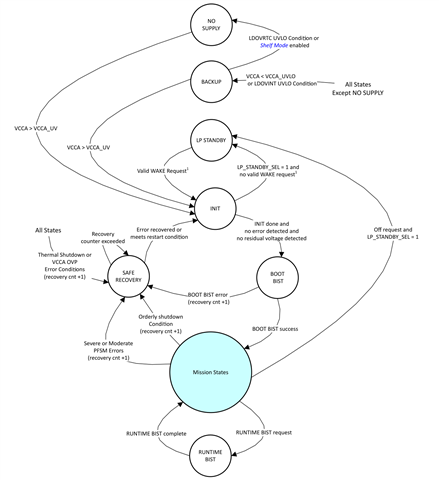

有时、我们的电路板根本不会出现。 我们发现一条用于控制的 SoC GPIO 线

在这些情况下、STM32_NRST 引脚被主动驱动为低电平。 我们甚至尝试了设置 A

该引脚上确实有强上拉、但 SoC 仍会将其驱动为低电平。

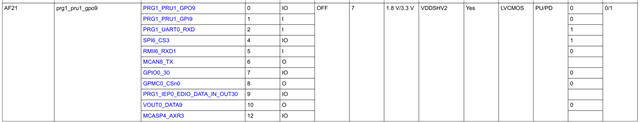

查看数据表、该引脚(AF21)应在复位时处于关断状态(高阻抗)。

我们如何看到这条线在复位时被主动驱动为低电平。 除非我、否则我无法使电路板正常工作

切换电源、进而释放引脚。

是否可以采取任何措施来确保该引脚在复位时"释放"?

此致、

/BO