工具/软件:

在 SDK 9.2中测试我们的模型时、 我们确定了以下三个问题:

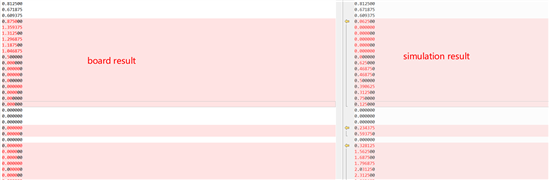

- 结果因电路板和仿真而异(UNCASTION_board_and_simulation 文件夹)

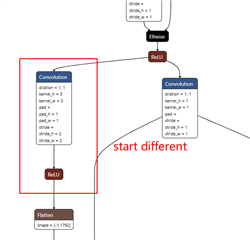

- 当我们在提供的网络输出层上添加一个简单的自定义层时、 电路板和 仿真的结果会有所不同、但当我们在其他网络之后添加相同的自定义层时(UNCASTIC_board_and_simulation_after_add_custom_layer 文件夹)、结果始终是正确的

- 自定义图层可以删除 pad,但我们发现自定义图层的输出 pad( cannot_remove_pad 文件夹)有时仍然存在。

为了便于验证这些问题、我们提供了定制层的模型和代码(位于 thec7x-mma-tidl 文件夹中)。 我们使用的 SDK 版本为 SDK9.2、我们使用的 ti_dl 版本为10.1。 我们在文件夹中提供复制材料,我们希望它能尽快解决。

复制材料链接:

/cfs-file/__key/communityserver-discussions-components-files/791/reproduction_5F00_materials.zip

谢谢!