主题中讨论的其他部件:、 sysconfig

工具/软件:

e2e.ti.com/.../hinduja_5F00_cluster_5F00_mpu_5F00_board_5F00_v1.2.pdf

尊敬的团队:

我附上了仪表组项目基于 AM62P 微处理器的原理图设计的 PDF。 我们目前处于设计验证阶段、非常感谢您提供反馈。

您可以查看原理图并提出任何必要的更改或改进建议吗? 随着我们的进步、您的指导将非常有帮助。

谢谢你。

此致、

Vandana D.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

e2e.ti.com/.../hinduja_5F00_cluster_5F00_mpu_5F00_board_5F00_v1.2.pdf

尊敬的团队:

我附上了仪表组项目基于 AM62P 微处理器的原理图设计的 PDF。 我们目前处于设计验证阶段、非常感谢您提供反馈。

您可以查看原理图并提出任何必要的更改或改进建议吗? 随着我们的进步、您的指导将非常有帮助。

谢谢你。

此致、

Vandana D.

你好 Vandana

感谢您发送原理图审阅申请。

您能否确认是否曾与任何 TI 销售部门合作。

如果是、请与 TI 销售合作提交原理图审核申请。

可以参考以下文档来执行自我审查

定制电路板自我审查和设计的推荐参考资料

AM62P

转换时间

AM62Px Sitara 处理器数据表

www.ti.com/.../sprsp89

硬件设计注意事项

www.ti.com/.../sprada9

DDR 电路板设计和布局布线指南

www.ti.com/.../sprad66

AM62Px 处理器系列的原理图设计和审阅检查清单

www.ti.com/.../spradn4

Sitara 处理器系列的原理图设计和审阅检查清单组合在一起

www.ti.com/.../sprad21

勘误表

www.ti.com/.../sprz574

原理图审阅申请(内部)

e2e.ti.com/.../4661966

AM62P 原理图检查清单

e2e.ti.com/.../faq-am625-am623-am62a-am62p-am62d-q1-am64x-am243x-design-recommendations-custom-board-hardware-design---schematics-review-checklists

AM62P 原理图自我审查

e2e.ti.com/.../faq-am62p-am62p-q1-design-recommendations-custom-board-hardware-design---custom-board-schematics-self-review

e2e.ti.com/.../faq-am625-am623-am62a-design-recommendations-commonly-observed-errors-during-custom-board-hardware-design-sk-schematics-updates-for-design-update-note

e2e.ti.com/.../faq-am625-am625-am623-am62a-am62p-am62d-q1-am64x-am243x-design-recommendations-custom-board-hardware-design---list-of-errors-observed-during-customer-schematics-review

e2e.ti.com/.../faq-am625-am623-am62a-am62p-am62d-q1-am64x-am243x-design-recommendations-custom-board-hardware-design---queries-related-to-soc 数据表引脚属性

常见问题解答

e2e.ti.com/.../faq-custom-board-hardware-design---master-complete-list-of-faqs-for-all-sitara-processor-am62x-am64x-am243x-am335x-families

e2e.ti.com/.../faq-am62p-am62p-q1-custom-board-hardware-design---faqs-related-to-processor-collaterals-functioning-peripherals-interface-and-starter-kit

e2e.ti.com/.../faq-am62x-am64x-custom-board-hardware-design-how-to-handle-used-unused-pins-peripherals-e-g-gpios-serdes-usb-csi-mmc-emmc-sd-card-csi-oldi-dsi

原理图 D-Note、R-Note 的常见问题解答

e2e.ti.com/.../faq-am62p-am62p-q1---custom-board-hardware-design---design-and-review-notes-for-reuse-of-sk-am62p-lp-schematics

可从 TI.com SK 列表下载的设计文件

SK-AM62P-LP 设计包文件夹和文件列表(修订版 A)

www.ti.com/.../sprt780

https://www.ti.com/lit/zip/sprr487

此致、

Sreenivasa.

你好 Vandana

谢谢 。

能否请您回答以下问题、以防您错过。

您能否确认是否曾与任何 TI 销售部门合作。

如果是、请与 TI 销售合作提交原理图审核申请。

[/报价]此致、

Sreenivasa.

你好 Vandana

为了使审核更有效、您能在设计中突出强调您希望提供意见或认为可能有改进空间的任何具体领域吗?

检查清单分为几个部分、供您重点介绍该部分和所关注的外设。

此致、

Sreenivasa.

你好 Vandana

我做了快速检查、发现引导模式可以得到优化

当不使用引导模式缓冲器时、您只能使用上拉或下拉电阻来配置和删除 DIP 开关。 这是推荐的方法。

请遵循上述常见问题解答。

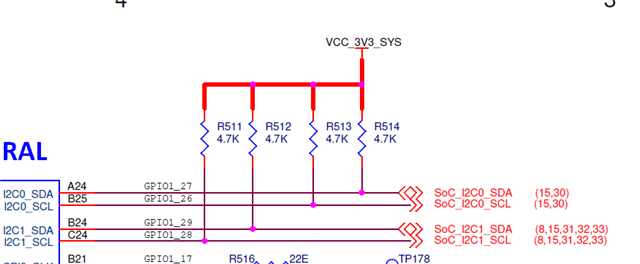

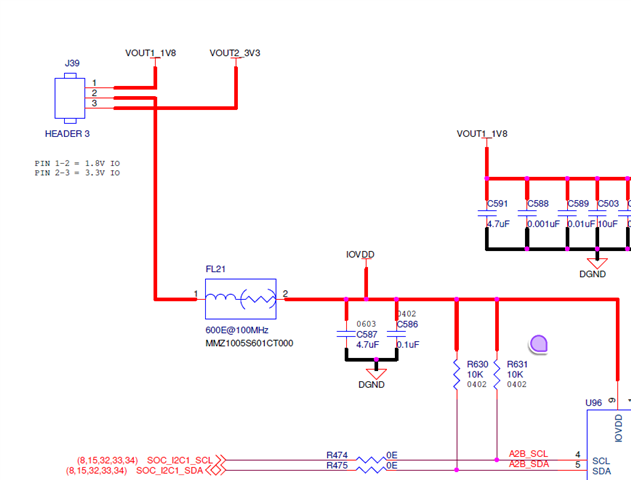

连接到 U96的 SoC_I2C1_SCL 在 SOC 附近有一个上拉电阻、

和

建议在一个位置上拉 I2C、并使电源轨与 IO 组 VDDSHV0的 IO 电源匹配。

此致、

Sreenivasa.

您好、 Vandana、

在将 SK 设计文件重复用于定制电路板设计时、请参阅以下常见问题解答:

此致、

Sreenivasa.

您好、 Vandana、

在将 SK 设计文件重复用于定制电路板设计时、请参阅以下常见问题解答:

此致、

Sreenivasa.

您好、Vandana、

根据快速回顾、我可能会提出一些额外的观察结果。

注意到。 如果需要进行任何其他更改、请告知我。

我将在下周初分享同样的内容。

此致、

Sreenivasa.

您好、Vandana、

注意到。 如果需要进行任何其他更改、请告知我。

本设计未使用 CSI 和 DSI

我看到了上面的注释。 请注意当这些外设不是您时的连接要求。

如果您需要配置、则应将这些信号路由为100R 差分对、并端接至与使用外设时可能进行的连接类似的连接器。

此致、

Sreenivasa.

您好、Vandana、

我做了一些快速检查、并将我的注释添加到原理图中。

请检查并更新注释。

一般备注(供客户审核)

e2e.ti.com/.../8512.hinduja_5F00_cluster_5F00_mpu_5F00_board_5F00_v1.2.pdf

此致、

Sreenivasa.

您好、Vandana、

请注意、我做了一些快速检查并添加了我的评论。

请与 TI 销售部门合作、获取有关遵循我在初始回复中分享的配套资料的任何其他支持。

一些通用指南

我们检查了原理图以确定最佳状态。 由于实施和设计流程是特定于客户的、

客户可能需要查看并进行更新的类似更新。

验证 SOC 的所有内核、模拟和 IO 电源是否连接到建议的电源电压电平

使用可调直流/直流或 LDO 时、请验证电阻分压器比率是否与所需的输出电压匹配

确保所有连接到 SoC 的上拉电阻器都上拉至正确的 I/O 电压(与以特定 IO 组为基准的 IO 电源匹配)

根据确认器件选择的要求验证数据表的器件选择部分

使用 SysConfig - pinmux 工具验证存储器接口、通信和 IO 接口的引脚配置

根据数据表的引脚属性部分、验证原理图符号引脚编号和名称以及引脚名称和编号的映射

任何连接了布线但未主动驱动的 SoC 焊盘都需要外部并联拉电阻

针对允许的引导模式配置和影响功能的勘误表、验证特定于器件的勘误表

验证数据表的引脚连接表是否连接任何未使用的引脚或外设(包括电源)

请通读 SOC 数据表中的引脚连接要求、并确保遵循相关建议

用于分立式直流/直流或 LDO 输出电源反馈的电阻分压器容差为1%、可提高输出精度

请注意 I2C 接口例外情况和引脚连接要求

添加隔离和探测 OBSCLK 以进行测试的配置

通用 SOC LVCMOS IO 接口指南(供客户审查和更新)

1.大多数 SOC IO 都没有失效防护功能。 在电源斜升之前、不应施加任何输入

SoC LVCOMOS IO 指定了压摆率要求、建议不要应用慢速斜坡输入或在输入端连接电容器

3.不建议在 LVCMOS IO 输出端连接一个> 22pF 的电容负载。 DNI 电容器或根据用例执行仿真。

4.复位期间 SoC IO 缓冲器关闭。 需要在由 SOC IO 驱动且可能悬空的所连接器件附近放置一个拉电阻

5.任何连接了布线的 SOC IO 都需要一个并联拉电阻。 当添加拉电阻是不可行时、请确保布线远离噪声信号

6.不允许或不建议连接具有可直接配置到电源或接地的替代功能的 SOC IO (包括引导模式输入)。

(客户可能遇到固件错误、并且错误配置了这些用于输入(而是将输出驱动为逻辑高电平)的 LVCMOS GPIO)

7.验证 SOC 输出的电容负载(当连接任何>22 pF (取决于用例、最大值)的电容值时、客户需要进行仿真)、

输入信号的压摆率(LVCMOS 输入压摆率应为1000ns 或更小)、IO 兼容性以及 SOC IO 与所连接器件之间的失效防护运行情况

此致、

Sreenivasa.

e2e.ti.com/.../5700.hinduja_5F00_daughter_5F00_board.pdf

先生、感谢您抽出宝贵的时间、为我们的 MPU 主板设计提供宝贵的反馈。

我现在附上了子板设计、这个设计之前无意中遗漏了。 澄清一下、40引脚连接器仅用于 OLDI 显示、不用于调试。

您好、Vandana、

谢谢你。

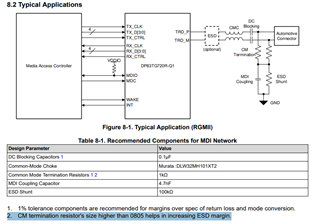

您需要参考介质转换器设计

https://www.ti.com/lit/ug/snlu289/snlu289.pdf

R18、R25 2 CRCW08051M00JNEA 电阻器、1.0M、5%、0.125W、AEC-Q200 0级、 0805 0805_HV

C7、C28 2 GRM31BR73A472KW01L 电容器、陶瓷、4700 pF、1000V、+/-10%、 X7R、1206

数据表参考

https://www.ti.com/lit/ds/symlink/dp83tg720r-q1.pdf

此致、

Sreenivasa.

您好、Vandana、

另外、一个快速提醒、 您有机会回顾我们的子板原理图。

SOM 板与子板之间的信号不会映射。

请提供一个表来查看从 SOC 板到子板的信号。

此致、

Sreenivasa.

e2e.ti.com/.../0871.hinduja_5F00_daughter_5F00_board.pdf

您好、Vandana、

谢谢你。

我从我这边添加了快速回顾评论。

请审核并进行必要的更新、同时与相关 PLS 合作以审查实施情况。

此致、

Sreenivasa.