Thread 中讨论的其他器件: TDA4VH

工具/软件:

您好、

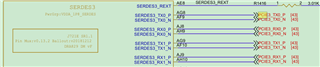

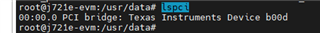

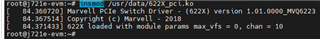

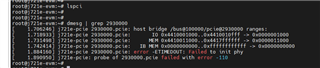

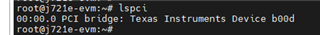

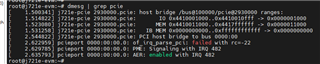

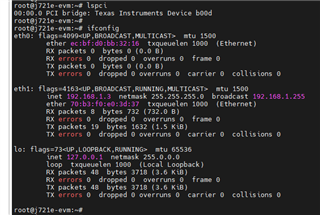

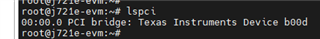

我在 Linux 中添加了 PCIe 配置、并在启动后使用 lspci 命令输出以下内容:

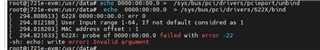

但当我使用以下命令时、它似乎会报告失败的问题:

是否存在导致此错误的配置问题? 我知道、在完成配置并加载驱动程序后、lspci 可以识别两个节点

此致、

Yang

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Yang:

'OF_IRQ_PARSYS_PCI:失败、RC=–22'可以忽略。 从功能上讲、这不应导致任何问题。

但是、如果您想删除该错误、下面是将集成到下一版本 SDK 中的补丁:

https://patchwork.kernel.org/project/linux-pci/patch/20240726135903.1255825-1-s-vadapalli@ti.com/

此致、

Takuma

您好、

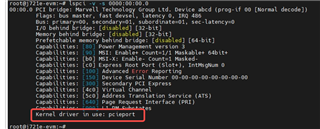

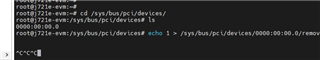

今天我做了一些新的修改和测试。 我尝试将 PCIe 驱动程序绑定到新添加的 MVL 驱动程序。

echo 0000:00:00.0 > /sys/bus/pci/drivers/pcieport/unbind

echo 0000:00:00.0 >/sys/bus/pci/drivers/622X/bind

我想知道以下问题:

1.使用外部交换机时是否应该修改当前的 PCIe 绑定内核驱动程序?

2.如果第一个问题是必要的,上述步骤是否正确?

3.应如何解决以上报告的错误?

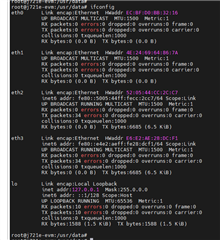

4.完成所有配置后、PCIe 是否应生成一个类似于下图所示的 ETH 节点?

5.据我所知,我已经完成了 PCIe 节点的生成。 您能否提供有关如何匹配外部交换机芯片以及需要配置什么的完整说明?

此致、

Yang

您好、

添加文件。

e2e.ti.com/.../lspci-_2D00_vvv-_2D00_s.txt

此致、

Yang

尊敬的 Yang:

很多问题,所以我会把我的答复分成两篇文章。 第一篇文章直接回答所观察到的问题和行为分析。 第二篇文章将是我怀疑正在发生的事情,以及在哪里检查。

[引述 userid=“572765" url="“ url="~“~/support/processors-group/processors/f/processors-forum/1506597/tda4vm-some-pcie-questions/5791497 #5791497“]我还有一个问题。 我正在使用 Seder3、但如果执行以下命令、并且日志是 Seder2 pcie2920000 的地址、为什么会这样?

[/报价]如果您说的是真的并且使用了 PCIe3、则不应发生这种情况。 从软件角度来看、PCIe2 已启用、而不是 PCIe3。

1. 使用外部交换机时是否应该修改当前的 PCIe 绑定内核驱动程序?

2.如果第一个问题是必要的,上述步骤是否正确?[/报价]可以选择手动绑定内核模块。 一般的解除绑定/绑定方法是 正确的、但我认为您将驱动程序绑定到 PCIe 端口而不是交换机设备。

例如、这是当 NVMe SSD 卡连接到端口时、TDA4VH(应与 TDA4VM 相同)上的预期结果:

e2e.ti.com/.../lspci_5F00_example_5F00_j784s4.txt

在上面的 lspci 日志中有一个“PCI 桥接器“设备和一个“非易失性内存控制器“设备。 桥接器应保持不变、内核模块应绑定到桥接器下显示的器件(未显示)。

另外请注意、假设启动时加载了内核模块、内核模块应使用器件和供应商 ID 自动绑定到正确的 PCIe 器件。 因此、手动绑定方法是一种通常不需要的替代方法、除非您从头开始开发新的内核模块、或者它是一个不自动绑定的演示内核模块。

[/quote]3. 应如何解决上面报告的错误?

[/报价]错误 22 指向无效参数。 这很可能是由于绑定到错误的器件造成的。

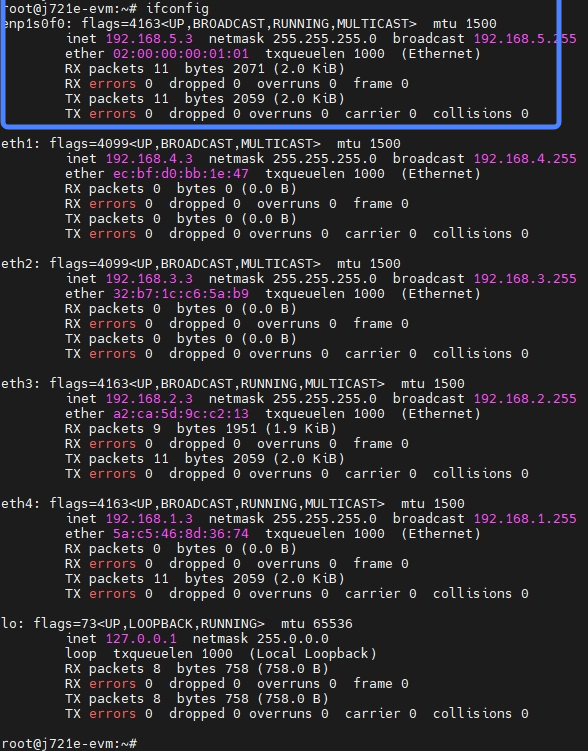

[引述 userid=“572765" url="“ url="~“~/support/processors-group/processors/f/processors-forum/1506597/tda4vm-some-pcie-questions/5792422 #5792422“]4.完成所有配置后、PCIe 是否应生成一个类似于下图所示的 ETH 节点?

[/报价]是的、内核模块驱动程序 应在 ifconfig 下枚举。 我 以前没有查看过这个特定的驱动程序、但 我看到的所有 PCIe 以太网交换机驱动程序都已经查看过。

此致、

Takuma

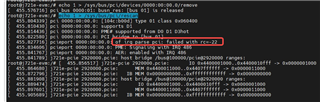

我怀疑发生的情况是、根据以下语句在器件树中配置了错误的 PCIe 实例。

此外、我还有另一个问题。 我正在使用 Seder3、但如果执行以下命令、并且日志是 Seder2 pcie2920000 的地址、为什么会这样?

在任何情况下、如果您可以执行 1 和 2、我可以检查器件树以了解上面的步骤 3 中列出的内容。

此致、

Takuma

您好、

无论如何、如果可以执行 1 和 2、我可以查看器件树以了解上面的步骤 3 中列出的内容。

e2e.ti.com/.../PCIE_5F00_DTS.diff

请注意、假设内核模块在引导时加载、内核模块应使用器件和供应商 ID 自动绑定到正确的 PCIe 设备。 因此,手动绑定方法是一种通常不需要的替代方法,除非您从头开始开发一个新的内核模块,或者它是一个不会自动绑定的演示内核模块。

如果您说的是 true 并且使用了 PCIe3、则不应发生这种情况。 在软件方面似乎启用了 PCIe2 而不是 PCIe3。

此致、

Yang

尊敬的 Yang:

执行以下操作:

我认为问题是 PCIe 控制器正在枚举、但连接到 PCIe 控制器的设备(在本例中为以太网交换机)未枚举。 上述建议将有助于缩小没有枚举的原因。

此致、

Takuma

您好、

您是否还可以共享“dmesg"中“中的完整日志?

您能否将 vendor-id 和 device-id 更改回 PCIe3_RC 中的原始格式? [/报价]

- 即使恢复到其原始值、仍然没有 ETH 节点。

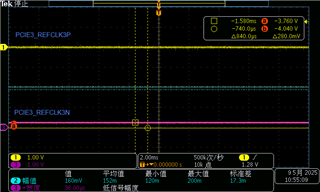

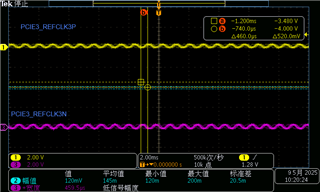

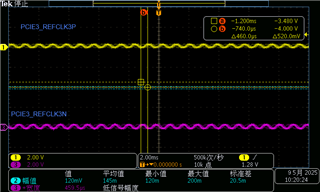

查看是否有 100MHz 基准时钟提供给开关我通过示波器检测到 PCIe3-REFCLK 信号、发现没有波形。

此致、

Yang

[/quote]

您好、

我还有一些其他问题。

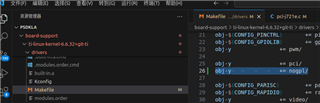

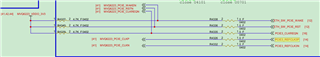

1、如果我在下图中修改 u-boot 的配置文件、那么在执行 make all 和 make install 后、是否需要将新的 u-boot.img 映像复制到 SD 卡?

我仅复制了以下两个命令、然后使用 lspci 命令查看已生成的 PCIe 节点。

out/evm/targetfs/boot/dtb//media/master/root/boot

out/evm/targetfs/boot/Image /media/master/root/boot

2 μ s 当我在、中添加 clk 配置时、我发现 PCIe3 节点报告了错误。

此致、

Yang

尊敬的 Yang:

dmesg 日志有点奇怪。 看起来 PCIe 控制器正尝试在单个引导中多次初始化。 我以前没见过这种情况... 但没有报告明显错误。 我确实注意到、重新初始化仅适用于 PCIe0、1 和 2。 PCIe3 看起来会按预期初始化一次。

如果 PCIe3 是唯一使用的 PCIe 接口、您是否可以尝试从器件树中删除 PCIe0、1 和 2 节点来清理日志?

即使恢复到其原始值、仍然没有 ETH 节点。

这是预期结果。 PCIe 控制器正常工作、但不存在初始化以太网交换机的问题。

I 通过示波器检测到 PCIe3-REFCLK 信号、发现没有波形

这就是问题所在。 可能是它不输出参考时钟的几个原因。 对于初学者、您是否可以尝试应用此补丁:

此致、

Takuma

您好、

很抱歉晚才回复。 我已阻止器件树中的 PCIE0/1/2 节点并添加了您提供的补丁、但在测试过程中仍然没有生成 PCIe.CLK。

以下补丁是我所做的修改:

e2e.ti.com/.../5381.PCIE_5F00_serder3.diff

以下是添加的修改后的 dmesg 信息:

e2e.ti.com/.../dmesg_5F00_log1.txt

此致、

Yang

您好、

以下是我们使用的器件树文件。 您可以检查是否有任何内容配置不正确。

e2e.ti.com/.../0045.dts.tar.gz

此致、

Yang

尊敬的 Yang:

您是否可以尝试应用此修补程序:

此致、

Takuma

您好、

[引述 userid=“492487" url="“ url="~“~/support/processors-group/processors/f/processors-forum/1506597/tda4vm-some-pcie-questions/5804492 #5804492“]您是否可以尝试应用此修补程序:

0001-ADD-ACSPCIE-BUFFER-CONTROL-FOR-ENABLE-clock-pBuffer.patch

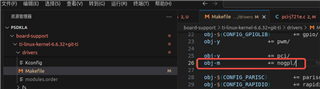

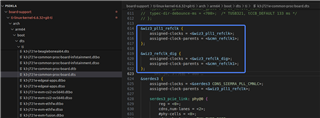

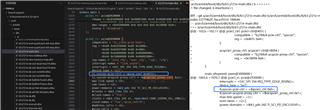

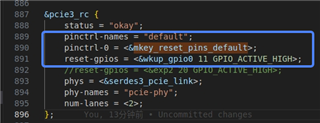

[/报价]我已经尝试了该补丁、但仍然没有 CLK 波形。 但是、我注意到此贴片与当前的设备树之间存在一些差异、我不确定这是否会产生任何影响。 如下图所示:

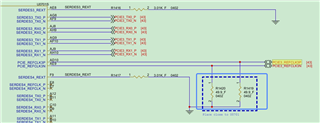

此外、我注意到 CLK 的原理图中有一个连接、如下图所示。 我想知道这是否会影响其功能?

此致、

Yang

尊敬的 Yang:

我已经尝试了该补丁、但仍然没有 CLK 波形。 但是、我注意到此贴片与当前的设备树之间存在一些差异、我不确定这是否会产生任何影响。 如下图所示:

这也是奇怪的。 我认为在之前的 E2E 主题中添加了 PCIe3_ctrl、但或许补丁中漏掉了这些 PCI。

是否可以添加以下内容:

pcie3_ctrl: pcie3-ctrl@407c {

compatible = "ti,j784s4-pcie-ctrl", "syscon";

reg = <0x407c 0x4>;

};pcie3_rc: pcie@2930000 {

compatible = "ti,j721e-pcie-host";

reg = <0x00 0x02930000 0x00 0x1000>,

<0x00 0x02937000 0x00 0x400>,

<0x00 0x0e800000 0x00 0x00800000>,

<0x44 0x10000000 0x00 0x00001000>;

reg-names = "intd_cfg", "user_cfg", "reg", "cfg";

interrupt-names = "link_state";

interrupts = <GIC_SPI 354 IRQ_TYPE_EDGE_RISING>;

device_type = "pci";

ti,syscon-pcie-ctrl = <&pcie3_ctrl 0x0>;

max-link-speed = <3>;

num-lanes = <2>;

power-domains = <&k3_pds 242 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 242 1>, <&serdes3 CDNS_SIERRA_PLL_CMNLC>;

clock-names = "fck", "pcie_refclk";

#address-cells = <3>;

#size-cells = <2>;

bus-range = <0x0 0xff>;

vendor-id = <0x104c>;

device-id = <0xb00d>;

msi-map = <0x0 &gic_its 0x30000 0x10000>;

dma-coherent;

ranges = <0x01000000 0x0 0x00001000 0x44 0x10001000 0x0 0x0010000>,

<0x02000000 0x0 0x00011000 0x44 0x10011000 0x0 0x7fef000>;

dma-ranges = <0x02000000 0x0 0x0 0x0 0x0 0x10000 0x0>;

status = "disabled";

};此外、我注意到 CLK 的原理图中有一个连接、如下图所示。 我想知道这是否会影响其功能?

[/报价]这看起来很好。

在 u-boot 中对 vNet of_LIBFT_SVERLAY=y 进行注释后、我发现可能生成的 eth1 节点消失了、无法再查看 R5F 内核的日志。

这可能是由于不再应用覆层。 是否有 U-Boot 使用的 uEnv.txt 中定义的器件树重叠?

此致、

Takuma

尊敬的 Yang:

[引述 userid=“572765" url="“ url="~“~/support/processors-group/processors/f/processors-forum/1506597/tda4vm-some-pcie-questions/5807463 #5807463“]下图显示了 uEnv。 TXT、我是否需要进行任何修改?

[/报价]我认为这解释了为什么我们需要 在前一个线程中删除 of_LIBFDT_overlay。 覆盖层很可能覆盖了 SERDES_ln_ctrl 节点。

您能否在 k3-j721e-evm-ethfw.dtso 中将 SERDES3 通道修改为 PCIe、重新编译并刷写新的 dtbo 文件? https://git.ti.com/cgit/ti-linux-kernel/ti-linux-kernel/tree/arch/arm64/boot/dts/ti/k3-j721e-evm-ethfw.dtso?h=ti-linux-6.6.y

这样、您可以放回 of_LIBFDT_OVERLATE、以太网实例应在 ifconfig 下再次出现。

此致、

Takuma

您好、

1、我将 k3-j721e-evm-ethfw.dtso 文件中的 serdes3 修改为 PCIe、并打开了 of_LIBFT_SVERLAY 宏定义、该宏定义也可以正常生成 PCIe 器件节点和 ETH 节点。

减少。 diff 文件是我修改的内容:

我发现、打开_LIBFT_SVERLAY 的宏定义后、我无法再删除生成的 PCIe 设备节点、这将导致系统出现

冻结、如下图所示:

2 μ s、、我找到了之前关于 PCIe CLK 的文章:

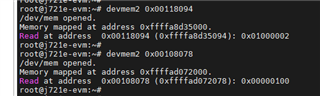

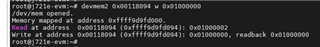

我尝试读取上述两个寄存器、发现 0x00118094 的值与预期值不匹配。 因此、我将其值修改为 0x01000000

发现 CLK 电平略有变化。

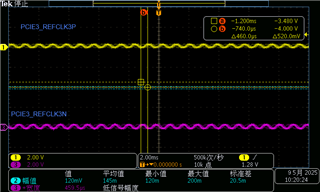

然后、 我 在 POST 中将 0001-PCIe-internal-refclk-patches-for-8.6-SDK-on-TDA4VM-J.patch 合并到当前代码中、并按照测量了波形

如下图所示:

上图是否是正常的 CLK 波形? 它们的电压值看起来仅为 300mV、并且尚未能够生成 PCIe ETH

应用手册。

此致、

Yang

尊敬的 Yang:

对于您的第 1 点、奇怪的是您无法再移除控制器。 但是、最好看到 eth 接口全都出现了。

对于您的第 2 点、看起来现在有一些时钟输出。 这很好。

此致、

Takuma

您好、

以下是 PCIe 控制器和 dmesg 信息:

e2e.ti.com/.../dmesg_5F00_log3.txt

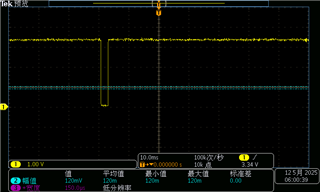

我按如下、配置并测量了 MVL_PACIE-RST 引脚、该引脚生成了 2.4ms 的拉低电平、此后保持高电平、但仍然未生成

新的 ETH 节点。

上图是否是正常的 CLK 波形? 它们的电压值看起来仅为 300mV、并且尚未能够生成 PCIe ETH

应用手册。

[/报价]我想知道该波形是否解决了无时钟的问题? 我们现在应该调查内容的哪些方面?

此致、

Yang

您好、

[引述 userid=“572765" url="“ url="~“~/support/processors-group/processors/f/processors-forum/1506597/tda4vm-some-pcie-questions/5810323 #5810323“]

上图是否是正常的 CLK 波形? 它们的电压值看起来仅为 300mV、并且尚未能够生成 PCIe ETH

应用手册。

[/报价]生成此处的波形时存在问题、即即使插入补丁后、我仍在 之后手动修改寄存器 0x00118094

打开电源进行更改。

此致、

Yang

尊敬的 Yang:

下面随附了 DTS、dtsi 和 Sierra SerDes 驱动程序、其中包含我们今天会议所做的更改和生成的时钟输出。 请随意进行比较、看看是否有差异。

e2e.ti.com/.../7331.k3_2D00_j721e_2D00_common_2D00_proc_2D00_board.dts

e2e.ti.com/.../k3_2D00_j721e_2D00_main.dtsi

e2e.ti.com/.../5773.phy_2D00_cadence_2D00_sierra.c

此致。

Takuma

您好、

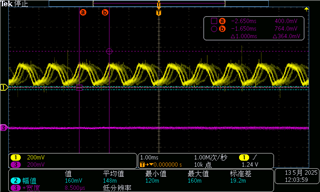

我比较了您提供的三个文件、与本地文件相比、PCIe 的配置内容没有差异、但当前的频率也没有差异

PCIe 的频率确实非常低。

以下是最新的 dmesg 信息和我通过使用命令 dcd -i fs -O dts -o extracte_device_tree.dts /proc/device-tree 解编译生成的 dts 文件 :

e2e.ti.com/.../dmesg_5F00_log4.txt

此致、

Yang

尊敬的 Yang:

i 比较了您提供的三个文件、与我的本地文件相比、PCIe 的配置内容没有差别、但目前的频率

确实很奇怪。

然后、我们来看看所有时钟、并在我的工作设置和您的设置之间进行比较。 下面是我的日志、来自“k3conf dump clocks > dump_all_clocks_pcie_internal_clock.txt“:

e2e.ti.com/.../dump_5F00_all_5F00_clocks_5F00_pcie_5F00_internal_5F00_clock.txt

您是否可以运行相同的文件并共享输出的 txt 文件?

此致、

Takuma

尊敬的 Yang:

我对 pcitest 程序有疑问。 如果我使用外部 MVL 交换机、我不能使用 pcitest 程序进行功能验证? 我使用了 pcitest.sh

否。 pcitest.sh 依赖于运行 PCI-EPF-TEST 内核驱动程序的 EP 端。 由于 交换机枚举为以太网接口、因此有不同的驱动程序绑定到交换机。

有关更多上下文信息:

如果执行“lspci -vv“、则每个不同 PCIe 设备的最后一行应包含“内核驱动程序正在使用“和“内核模块“信息。 如果使用的内核驱动器/模块用于 Linux Linux/RC EP 测试、则可以使用 pcitest.sh。 但是、我认为您已经成功地将 MVL Switch 驱动程序集成到 Linux 内核中、因此它应该会显示不同的内核驱动程序。 如果交换机工作正常、则 将由 pcitest.sh 测试的功能应该已经由交换机的内核驱动程序进行测试。

此致、

Takuma

您好、

我明白您的意思。 但我发现 PCIe 在反复启动 UFS 时可能出现安装失败。 您是否遇到过类似的情况

您最终遇到的问题?

以下是正常启动的 dmesg 日志:

e2e.ti.com/.../dmesg_5F00_log_5F00_normal.txt

以下是 PCIe 安装失败时的 dmesg 日志:

e2e.ti.com/.../dmesg_5F00_log_5F00_pcie_5F00_miss.txt

此致、

Yang

尊敬的 Yang:

[引述 userid=“572765" url="“ url="~“~/support/processors-group/processors/f/processors-forum/1506597/tda4vm-some-pcie-questions/5822894 #5822894“]但我发现 PCIe 在反复启动 UFS 时可能出现安装失败。 您是否遇到过类似的情况

[/报价]否、我之前未遇到此问题。

1.第一个问题:复制问题的过程是什么?

[引述 userid=“572765" url="“ url="~“~/support/processors-group/processors/f/processors-forum/1506597/tda4vm-some-pcie-questions/5822894 #5822894“]以下是 PCIe 安装失败时的 dmesg 日志:

[/报价]感谢您的日志。 至于日志、我看到检测到 PCIe 卡、但随后它会从以下两行中取消初始化:

链路断开的原因、我不知道。

2.第二个问题/请求:当 PCIe 卡未能枚举时,您是否可以尝试使用“echo 1 >/sys/bus/pci/rescan 手动运行总线扫描?

此致、

Takuma

您好、

[引述 userid=“492487" url="“ url="~“~/support/processors-group/processors/f/processors-forum/1506597/tda4vm-some-pcie-questions/5823665 #5823665“]感谢您的日志。 至于日志、我看到检测到 PCIe 卡、但随后它会从以下两行中取消初始化:

Q1: 这真的很奇怪,我目前找不到原因。

2. 第二个问题/请求:当 PCIe 卡未能枚举时、您是否可以尝试使用“echo 1 >/sys/bus/pci/rescan 手动运行总线扫描?

Q2: 事实上,我在上次发送的消息中尝试了操作,但我相信该命令最终失败了。 下图显示了上一项测试的内容;

该文件是我能够正常挂载 mvl 驱动程序时执行的命令的日志。

此致、

Yang

尊敬的 Yang:

实际上、我在上次发送的消息中尝试了该操作、但我相信该命令最终失败了。 下图显示了上一个测试的内容;

啊、我错过了。 是的、您好像已经尝试过、但没有连接 PCIe 接口。

在任何情况下,链接断开是奇怪的,因为 你看到网卡有时出现,所以软件方面,事情似乎是正确的。

您能否检查复位线路和基准时钟线路以查看在链路断开时它们是否处于活动状态?

此致、

Takuma

您好、

我通过在本地反复进行上电和断电复制了这个问题、并测试了 PCIe3 CLK 和复位引脚的状态、如下面的 tar 封装所示。

e2e.ti.com/.../8204.Status.tar.gz

此致、

Yang

尊敬的 Yang:

PowerPoint 中的错误 1 很可能会导致内核错误、因为 SoC 在 PCIe 器件初始化之前尝试访问 PCIe 器件存储器、这会导致总线错误、该错误是不可恢复的错误。 PowerPoint 似乎表明时钟没有初始化、但我不知道为什么会发生这种情况。 但似乎时钟有一些问题。

PowerPoint 中的错误 2 不会导致错误、但没有 PCIe 器件枚举、这是因为链路在初始化后断开。 我不知道为什么它会下降。

我会将此信息发送给硬件团队、看看他们是否有任何意见、但在此期间、您能否分享一些有关观察到的行为的详细信息:

从本质上讲、我想了解 观察到的每一种行为是否都 是罕见的问题、例如、1000 次中只有 1 次出现、还是 5 次中有 3 次发现的一个非常常见的问题。

此致、

Takuma

您好、

是的、我完全同意。 此帖子讨论了太多内容。

我已经打开了一个新的帖子: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1525866/tda4vm-some-pcie-questions

此致、

Yang