工具/软件:

我安装了 J721EXSOMXEVM 处理器卡的大型通用载板。 我正在通过与 TI XDS200 JTAG 探针的 JTAG 连接加载和运行程序。 我们已经使用此方法构建并运行其他代码。

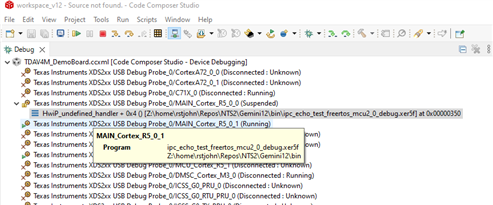

我尝试仅在两个 R5 内核上运行修改后的 IPC 回波示例。 主 MCU2_0 和主 MCU2_1。 (我不会在这个时候混淆 MCU 的命名。)

我选取了常用的 ipc_echo_test_fretos 示例、通过编辑这两个内核的“ipc_rtos_echo_test.c"文件“文件、将其限制在这两个内核、如下所示。

#if defined (SOC_J721E)

#define CORE_IN_TEST 1

.....

#ifdef BUILD_MCU2_0

uint32_t selfProcId = IPC_MCU2_0;

uint32_t remoteProc[] =

{

#if defined (SOC_J721E)

IPC_MCU2_1

.....

#ifdef BUILD_MCU2_1

uint32_t selfProcId = IPC_MCU2_1;

uint32_t remoteProc[] =

{

#if defined (SOC_J721E)

IPC_MCU2_0

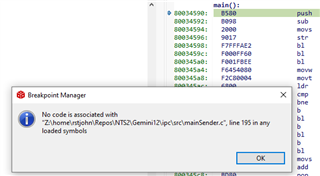

我花了一半时间与 Code Composer Studio 和调试器配合使用、另一半时间在汇编语言中设置断点、因为它拒绝让我在 C 代码中设置断点。