工具/软件:

您好:

我有一些与 UBoot R5 SPL 和 UBoot A72 SPL 的存储器使用情况相关的问题。

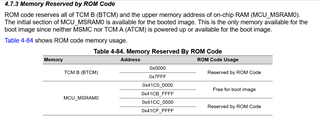

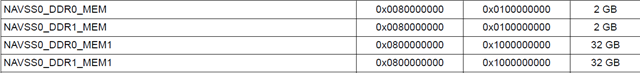

在构建 U-Boot R5 SPL 并检查相应的映射文件时、我找到起始地址 0x0000000080800000。 根据技术参考手册、这将是 DDR 存储器范围是否正确?

如果是、您能告诉我在 UBoot R5 SPL 运行之前哪个代码部分正在初始化 DDR 吗?

另外、在 UBoot A72 SPL 的链接器文件中、我在链接器脚本中看到以下定义:

内存{.SRAM : origin = 0x80080000

该地址是否真正位于 SRAM 中? 在参考手册中、我在哪里可以看到这一点?

提前非常感谢。