工具/软件:

在原始问题中 、我们收到了有关 如何访问 L1 高速缓存、L2 存储器和扩展 L2 存储器的信息。 现在、我们想知道如何从 C71x 代码访问 L3 存储器 (8MB 中央 MSMC RAM)。 您能否共享一个指向 J784S4 RTOS SDK 中的示例的指针(如果可用)或从 C71x 代码访问 L3 存储器的代码片段?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

在原始问题中 、我们收到了有关 如何访问 L1 高速缓存、L2 存储器和扩展 L2 存储器的信息。 现在、我们想知道如何从 C71x 代码访问 L3 存储器 (8MB 中央 MSMC RAM)。 您能否共享一个指向 J784S4 RTOS SDK 中的示例的指针(如果可用)或从 C71x 代码访问 L3 存储器的代码片段?

感谢 Brijesh 的答复。

您能否详细说明和/或分享一个示例、以便我更好地理解? 在 ti-processor-sdk-rtos-j784s4-evm-10_01_00_04/DSPLIB/cmake/linkers/C7120 中使用链接器文件时、您认为我是否需要使用以下 pragma 指令来访问 L3 存储器?

pragma DATA_SECTION(“.neardata")“)

请多多包涵。

嗨、Brijesh。 我们可以在这个主题上使用更基本的帮助、因为 TRM 对 C7X 存储器映射不太清楚。 在开发的这一阶段、我们主要关注使用此处 RTOS SDK 设置中所述的裸机设置进行 C7x 编程: 因此、software-dl.ti.com/.../ccs_setup_j784s4.html 不直接对与 C7x 相关的 MMU 进行编程、除非这是由调试脚本完成的。

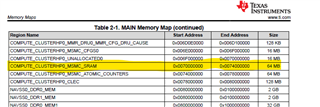

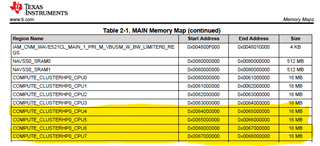

您能否介绍 TRM (www.ti.com/.../spruj52) 中的特定页面 、我们可以在其中找到有关 8MB MSMC3 SRAM 映射的 C7x 地址范围的信息?

表 2-1 存储器映射是否从 ARM 和 C7x 的角度反映了默认地址映射?

此外、8MB MSMC3 SRAM 是否映射到所有四个 C7x DSP 的相同地址范围、或者四个 C7X DSP 中的每个 DSP 是否有别名地址范围、如下所示的较低地址范围? 通过 CCS 实验、我可以看到地址 0x70000000 处有 SRAM、位于 C71X_0 和 C71X_1 之间。因此、我认为答案是肯定的、这是所有四个内核的相同共享地址、但请确认、或者更好的是、请向我们展示如何自己找到/确认该信息。

谢谢