https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1511793/am623-am623-dma

器件型号:AM623工具/软件:

尊敬的 TI 支持团队:

我正在查找与 AM62x 处理器上 DMA 功能相关的信息。

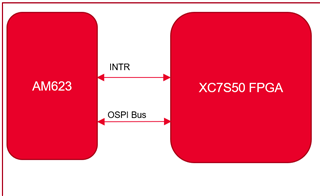

在我们的应用中、我们将 AM623 OSPI 连接到外部 FPGA。 计划是在从 FPGA 接收到中断时从 FPGA 检索一个包含多个 64 位数据的块。 我们想知道如何在从 FPGA 收到中断时触发 DMA 传输。

以下是我们目前遇到的问题。

- 是否有适用于 AM62x 的中断驱动 DMA 接口?

- 该接口是否可用于向存储器或外设高效写入数据或从存储器或外设高效读取数据?

- SDK 中是否有任何用于实现此类传输的建议驱动程序或示例?

您可以提供的任何文档或指导都会有所帮助。