Thread 中讨论的其他器件:TDA4VH

工具/软件:

我们尝试针对 C7x 上的向量运算复制 DSPLIB 用户指南性能一节中报告的周期计数、但结果不匹配。 我们的问题就在最后 下面是有关 我们设置的详细信息。

- 在 Ubuntu 22.04.1 主机上使用 J784S4 RTOS SDK 10.01.00.04

- 按照以下链接中的 DSPLIB 构建说明进行了操作: https://software-dl.ti.com/jacinto7/esd/processor-sdk-rtos-j784s4/10_01_00_04/exports/docs/dsplib/docs/user_guide/build_instructions_linux.html

- 已遵循以下链接中的 CCS 裸机说明: https://software-dl.ti.com/jacinto7/esd/processor-sdk-rtos-j784s4/latest/exports/docs/psdk_rtos/docs/user_guide/ccs_setup_j784s4.html#debugging-without-hlos-running-on-a72-rtos-only-baremetal

- 使用新的 J784S4XG01EVM 修订版 PROC141E5 (001)

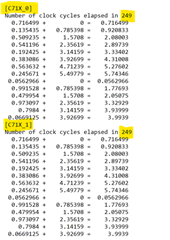

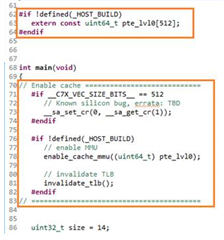

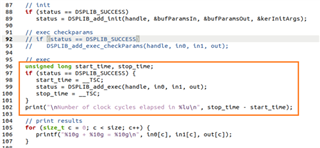

我们 在示例 DSPLIB_ADD (DSPLIB/examples/DSPLIB_add/) 中使用了 TSC 寄存器 DSPLIB_add_examples.cpp ) 如下面的代码片段所示、我们测量了以下内容。

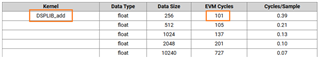

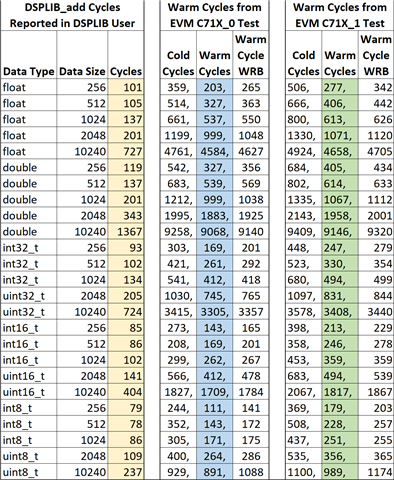

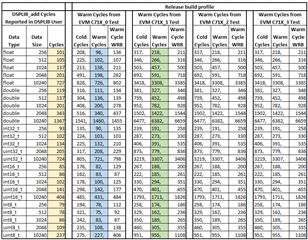

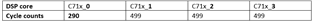

结果与 DSPBIL 用户指南(此处为 software-dl.ti.com/.../performance_summary.html

现在有几个问题。

- C71x_0 的运行速度始终快于其他 DSP 内核 (C71x_1/2/3)。 这是意料之外的、这是不是? 如果不是、这是 launch.js 脚本的工件吗?

- DSPLIB_ADD 是一个简单的示例、其中大小仅为 14。 因此、根据 DSPLIB 性能摘要、我预计 EVM 周期为~100、但是测量的值大约大 3 倍。 您能否帮助我了解 DSPLIB_add_examples.cpp 或 Build 命令中需要进行哪些更改才能在性能摘要中实现周期计数?