Thread 中讨论的其他器件: AM69、 SysConfig、 TDA4VH

工具/软件:

大家好、TI 专家。

我们正在使用基于 AM69A 的定制硬件平台、目前正在进行多次重新启动测试。

在此过程中、我们观察到两个反复出现的启动问题、它们会间歇性地阻止电路板启动:

1.由于频率握手超时而导致 SPL 挂起:

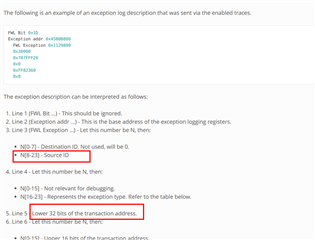

U-Boot SPL 2024.04-ti-gcedb677ccf6e (Apr 25 2025 - 10:55:48 +0000) SYSFW ABI: 4.0 (firmware rev 0x000b '11.0.9--v11.00.09+ (Fancy Rat)') Timeout during frequency handshake ### ERROR ### Please RESET the board ###

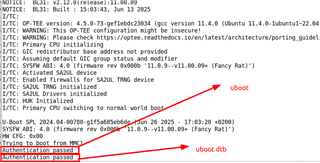

2. SPL 到 U-Boot 正确转换期间挂起:

U-Boot SPL 2024.04-34430-gf8c18ba41a3-dirty (May 16 2025 - 08:41:36 +0200) SYSFW ABI: 4.0 (firmware rev 0x000b '11.0.9--v11.00.09+ (Fancy Rat)') Initialized 4 DRAM controllers SPL initial stack usage: 13456 bytes HW CFG: 0x 0 Trying to boot from MMC1 Authentication passed Authentication passed Authentication passed Loading Environment from nowhere... OK init_env from device 17 not supported! Authentication passed Authentication passed Starting ATF on ARM64 core... NOTICE: BL31: v2.11.0(release):v2.11.0-906-g58b25570c9-dirty NOTICE: BL31: Built : 04:20:32, Nov 1 2024 I/TC: I/TC: OP-TEE version: 4.4.0-dev (gcc version 13.3.0 (GCC)) #1 Fri Oct 18 17:45:27 UTC 2024 aarch64 I/TC: WARNING: This OP-TEE configuration might be insecure! I/TC: WARNING: Please check optee.readthedocs.io/.../porting_guidelines.html I/TC: Primary CPU initializing I/TC: GIC redistributor base address not provided I/TC: Assuming default GIC group status and modifier I/TC: SYSFW ABI: 4.0 (firmware rev 0x000b '11.0.9--v11.00.09+ (Fancy Rat)') I/TC: Activated SA2UL device I/TC: Enabled firewalls for SA2UL TRNG device I/TC: SA2UL TRNG initialized I/TC: SA2UL Drivers initialized I/TC: HUK Initialized I/TC: Primary CPU switching to normal world boot U-Boot SPL 2024.04-34430-gf8c18ba41a3-dirty (May 16 2025 - 08:42:40 +0200) SYSFW ABI: 4.0 (firmware rev 0x000b '11.0.9--v11.00.09+ (Fancy Rat)') HW CFG: 0x 0 Trying to boot from MMC1 Authentication passed Authentication passed ------- Hangs here -------

我们的设计在 DDRSS 布局/配置和软件栈方面密切镜像了 AM69 SK 板。

我们在 TI E2E 论坛中遇到了一个潜在相关的问题:

https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1308890/tda4vh-q1-timeout-during-frequency-handshake/5211296#5211296

我们尝试了上述线程中的 DDRSS 参数更改、这略微改善了行为。 不过、与原始配置相比、相应的眼图显示信号完整性会下降、因此我们不打算在没有更有力证据的情况下采用这些变化。

您能帮助我们了解这些引导问题的潜在根本原因吗?

如有任何指导或建议、将不胜感激。

此致、

第 P 部分