工具/软件:

你(们)好

我们有一个具有一个 16b DDR4 的 AM6422。

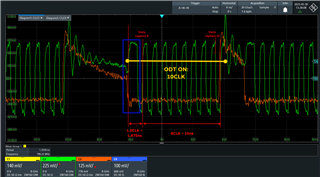

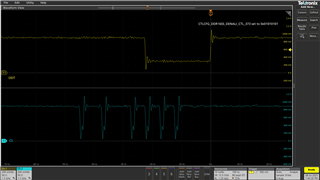

附加测量结果显示、 写入后的端接关闭得太早。、导致 DQS 对上出现振铃(绿色信号,测量差分)总置为有效时间是正确的(在本例中为 10CLK)、但似乎也过早激活了一点点。

我们将写入前导码设置为 1CLK、但看起来更像 1.5CLK...

这是如何改进的?

此致、

基督教

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

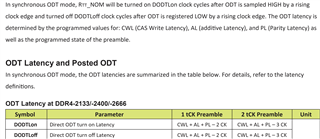

您好 Christian、我在 ISSI 规范中阅读了以下内容:

并且认为 CWL=11 会将延迟相对于 ODT 上升沿偏移 2 个时钟周期、但您是对的、我想整体会移动 2 个时钟周期。 您是否也能够捕获 ODT 信号?

我们可能需要调整配置、但我需要调查这是否可行。

同时、您可以尝试一件事、即配置中的此更改:

#define DDRSS_CTL_417_DATA 0x010 0 0001

看看这是否会使 ODT 激活移动。 这会调整与 ODT 信号相关的参数、但我对该位的描述有限、因此不确定它是否会有所帮助。

此致、

James

尊敬的 Christian:

好的、回顾延迟设置、对于 DDR4-2400 速度频段、您可以选择 CL=13 或 14(并且 CWL =9 或 11)。 您选择 CL=13 是否有原因?

我认为在过去的设计中、ISSI 器件的较高延迟设置带来了更好的结果。 我不知道确切的原因,但这可能必须由内存供应商解释。 可能由于我们在指定频率范围的边缘运行 、存储器中似乎存在与 DODTLon/off 相关的一些时序问题

换言之、您是否在另一个字节的其中一个数据位上看到了同样的问题? 我想知道一个字节的训练与另一个字节的训练是否不同、从而导致不同的延迟设置。 一个字节和另一个字节之间的布线长度是否明显不同? 您提到您有一个 16b DDR、所以我不认为是这样。

您能否提供 DDR 寄存器转储、以便我可以检查训练结果。 如果您使用 u-boot、则可以按照此处所述添加补丁:

此致、

James

您好、James。

´ll 实现该寄存器转储并返回结果。

之所以选择 CL13、是因为我们认为与 CL14 相比、这将带来稍高的性能。

同时、我搜索其他选项来优化 ODT 时序、并发现一个有趣的位:

CTLPHY_WRAP__CTL_CFG__CTLCFG_DDR16SS_DENALI_CTL_373 寄存器 (0F30 85D4h):

“

EN_ODT_ASSERT_EXCT_RD

除读取期间外、使控制器始终将 ODT 置为有效。

假设连接了单个 ODT 引脚。 设置为 1 可启用。

“

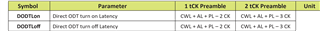

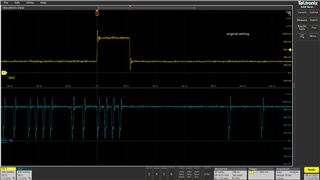

我对此进行了测试并获得了附加结果(原始设置和更改了 ODT 置位模式)。 因此、这似乎解决了在写入过程中提前关闭 ODT 的问题。 另一方面、我们现在必须在读取期间足够快地检查 ODT 是否禁用。

您是否担心使用此功能?

您好、Chris、

该位旨在仅与 LPDDR3 设计一起使用(控制器 IP 能够支持多种 DDR 类型、我们只支持 DDR4/LPDDR4)、因此即使您看到行为发生了变化、我也不建议使用。

我回头看了您的原始示波器屏幕截图。 您如何知道端接已提前启用? 从这张照片上可以看出、它只是过早地被禁用了。 什么是橙色信号? 如果是 ODT、似乎会反转、但我不明白为什么会悬空为 1/2 Vs

还有好奇您是否看到任何功能故障?

此致、

James

您好、James。 请找到随附的寄存器转储。

此致、基督教

您好、Christian、抱歉耽误了时间。

我检查了寄存器转储、看起来所有训练步骤都通过了。

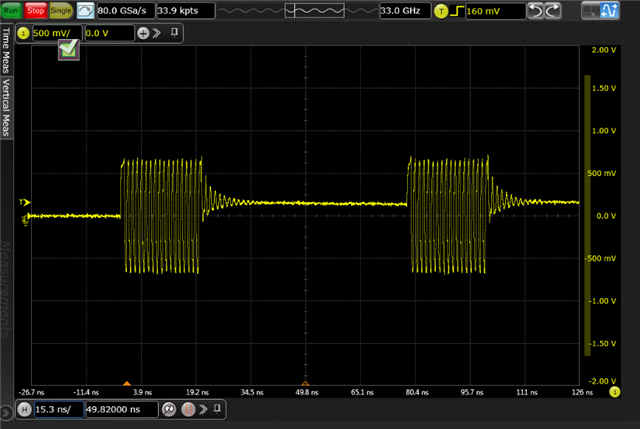

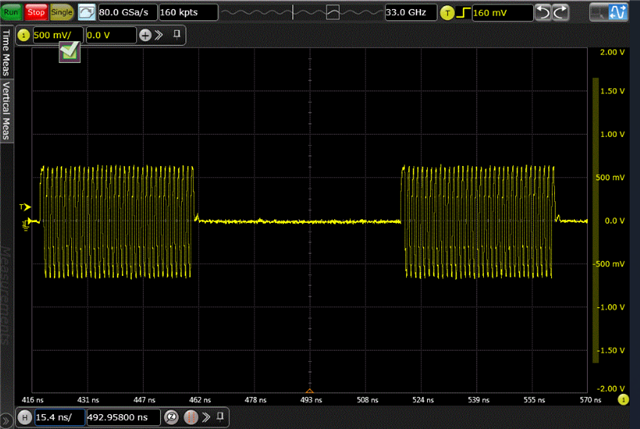

我还向同事展示了您的一些示波器镜头。 他确实提到了写入前导码的 1.5tCK 宽度符合 JEDEC 规范最小值 0.9tCK、宽度与我们在验证中看到的宽度类似。 此外、我们确实在突发结束时看到了一些振铃(见下文)

该功能通过启用 RTT Park 来抑制该功能

请注意、我们没有在启用 RTT PARK 的情况下验证操作、因为在禁用 RTT PARK 的情况下它可以正常工作。 但是、您可能要看看是否要对此进行实验、看看它是否会影响您的 EMI。

没有可从寄存器配置工具中更改 RttPARK 的选项。 但是、您可以手动修改配置文件。 DDR4 控制器使用的 MR5 值位于以下寄存器中:

CTL_236、PI_302

您将在其他寄存器中看到相似的值、但这些值不需要更改、并且与 DDR4 模式下的控制器无关。

此致、

James