主题中讨论的其他器件:J722SXH01EVM、 BeagleY-AI

工具/软件:

您好、

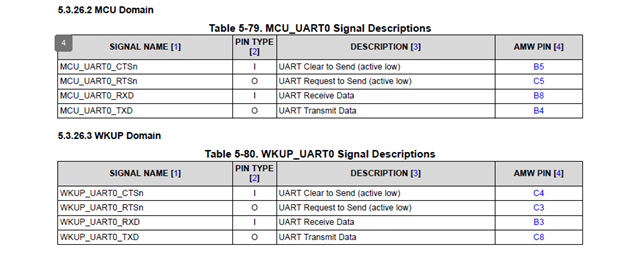

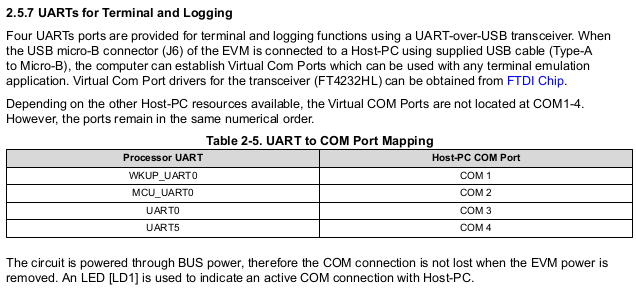

在评估板 J722SXH01EVM 上、我看到 J722S 的以下 UART 端口连接到 FTDI FT4232HL(每个端口都在 RTSN/CTSN 之外):

A) F19/F20 (UART0_TXD/RXD)

b) C8/B3 (WKUP_UART0_TXD/RXD)

C) B4/B8 (MCU_UART0_TXD/RXD)

D) H27/J27 (SOC_UART5_TXD/RXD)

您能否给出设计新电路板和进行软件开发所需的参数。

(设计电路板时不会出现像 FTDI 芯片这样的 UART 转 USB 桥接器、我们可能还需要调试 R5 tispl.bin-uboot)。

该用例包括“从 UART 和闪存固件引导“和“MCU R5F 应用程序运行时调试 UART 打印“。

1.A)+ B)

2.A)+ B)+ C)

3.a) 仅(通过更改固件将输出重新路由到此位置)

4、所有的 A) B) C) D)(我认为 D 不是很需要)

尽可能减少首选的引脚数。

我们选择了选项 3。 引导代码 (R5 端 uboot) 或 MCU R5F 应用程序 UART 调试会使开发复杂化吗?

请提出建议。

BeagleY-AI 的布局 (UART) 将 F19/F20 放置在 JST 3 引脚接头之一、并将一个 Linux 控制台分配给其 USB-C 端口、

其他(应用用)UART 转至 40 引脚扩展头、就像看起来一样。 R5 tispl.bin 控制台打印输出是否路由到 BeagleY-AI 上的 F19/F20?

提前感谢!

我正在查看的页面:

* 3.1.9.1.从控制台 UART 引导 U-Boot