主题中讨论的其他器件:AM2432

工具/软件:

您好团队:

我使用 AM2432 和 de83822 开发 EtherCAT 子器件应用。

链路检测通过 MDIO 正常工作、但通过 PHY 的 GPIO 无法正常工作。

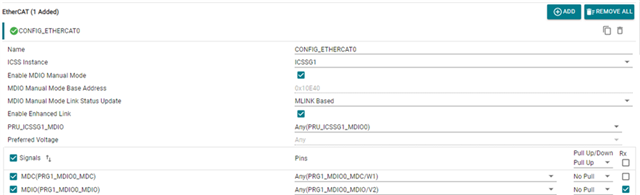

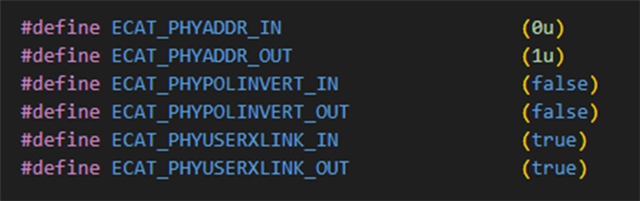

这就是我设置它的方式。

但是、不仅不会检测到链路、甚至不会找到链路。

是否需要任何其他配置?

最好的注意、

Oyama

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好团队:

我使用 AM2432 和 de83822 开发 EtherCAT 子器件应用。

链路检测通过 MDIO 正常工作、但通过 PHY 的 GPIO 无法正常工作。

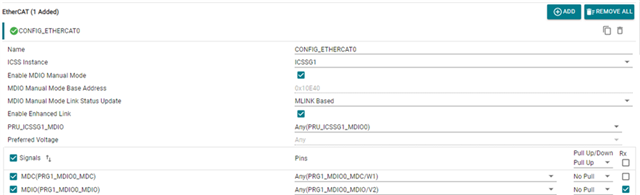

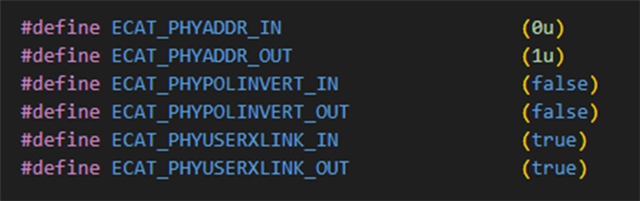

这就是我设置它的方式。

但是、不仅不会检测到链路、甚至不会找到链路。

是否需要任何其他配置?

最好的注意、

Oyama

您好、

但是、不仅无法检测到链接、还无法找到链接。

#define ECAT_PHYUSERXLINK_IN (false) #define ECAT_PHYUSERXLINK_OUT (false)

此致、

Aaron

您好、

是的。

感谢您的确认。 因此问题似乎在于增强链路配置。

该值为 0x02、但实际连接的端口仅为 0x01。

也许链路极性反转、以便在连接端口之前 0x300B240C 为 0x03、在连接 IN 端口时变为 0x02(位 0 复位)。 或者、如果极性未反转、则尝试根据 MDIO 链路寄存器中的链路状态(即 1 表示输入、0 表示输出)配置 SYSCFG 中的 PHY 地址。

此致、

Aaron

您好 Aaron、

我应用了更新、将 ECAT_PHYPOLINVERT 设置回 false(实际波形也为低电平有效)、链路和 EtherCAT 通信现在正常工作。

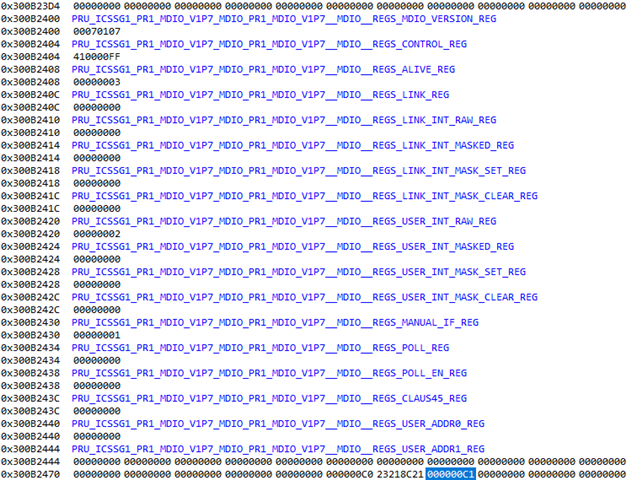

此外、当 IN 和 OUT 端口均连接到 AM243x 器件时、您是否能够提供完整的 ICSS MDIO 存储器转储 (0x300B2400 至 0x300B248C) 以及 PHY 寄存器值。

在初始步骤中、我将 MDIO_POLL_EN_REG (0x300B2438) 更 改为 0。

最好的注意、

Oyama

| phy0 (in) | phy1 (out) | |

| 0x0000 | 0x3100 | 0x3100 |

| 0x0001 | 0x786d | 0x786d |

| 0x0002. | 0x2000 | 0x2000 |

| 0x0003 | 0xA240 | 0xA240 |

| 0x0004. | 0x01E1 | 0x01E1 |

| 0x0005. | 0xC1E1 | 0xC1E1 |

| 0x0006. | 0x000F | 0x000F |

| 0x0007 | 0x2001 | 0x2001 |

| 0x0008. | 0x4000 | 0x4000 |

| 0x0009. | 0x0080 | 0x0080 |

| 0x000A | 0x0132 | 0x0132 |

| 0x000B | 0x1000 | 0x1000 |

| 0x000C | ||

| 0x000D | 0x401F | 0x401F |

| 0x000E | 0x0024 | 0x0024 |

| 0x000F | 0x0000 | 0x0000 |

| 0x0010 | 0x0215 | 0x4215 |

| 0x0011 | 0x0108 | 0x0108 |

| 0x0012 | 0x6400 | 0x6400 |

| 0x0013 | 0x2800 | 0x2800 |

| 0x0014 | 0x0000 | 0x0000 |

| 0x0015 | 0x0000 | 0x0000 |

| 0x0016 | 0x0100 | 0x0100 |

| 0x0017 | 0x0049 | 0x0049 |

| 0x0018 | 0x0200 | 0x0200 |

| 0x0019 | 0x8C20 | 0x8C21 |

| 0x0025 | 0xC1E1 | 0xC1E1 |

您好、

I 应用了更新并将 ECAT_PHYPOLINVERT 设置回 false(实际波形也为低电平有效)、链路和 EtherCAT 通信现在正常工作。

感谢您的确认。 我们能否将该主题标记为“已解决“?

在初始步骤中、我已将 MDIO_POL_EN_REG (0x300B2438) 更 改为 0。

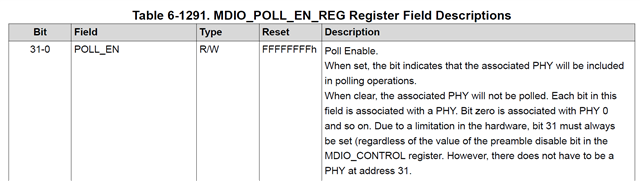

如 TRM 中所述、建议设置 MDIO_POLL_EN_REG 中的位 31 以消除硬件限制:

此外、由于您的应用中选中了“Enable MDIO Manual Mode“、因此还可以 分别在 0x30090E48 和 0x30090E4C 处监控 MDIO_LIVE_REG 和 MDIO_LINK_REG。

此致、

Aaron