主题中讨论的其他器件: DRA821、 TDA4VH

工具/软件:

您好 TI

我使用 DRA821U EVM (J7200)、SDK 版本为 10_01_08_01

我可以在内核空间中启用 USB3 功能、我就可以了。 但 uboot 中的相同设置不起作用。

U-boot 日志:

U-Boot SPL 2024.04-gb40fba1b-dirty (2025年5月05日- 11:31:08 +0800)

SYSFW ABI:4.0(固件版本 0x000a '10.0.8--v10.00.08 (Fiery Fox)')

尝试从 MMC2 引导

警告:在 GP 设备上检测到映像签名证书。 跳过证书以防止启动失败。 如果映像也经过加密、此操作将失败

警告:在 GP 设备上检测到映像签名证书。 跳过证书以防止启动失败。 如果映像也经过加密、此操作将失败

警告:在 GP 设备上检测到映像签名证书。 跳过证书以防止启动失败。 如果映像也经过加密、此操作将失败

警告:在 GP 设备上检测到映像签名证书。 跳过证书以防止启动失败。 如果映像也经过加密、此操作将失败

警告:在 GP 设备上检测到映像签名证书。 跳过证书以防止启动失败。 如果映像也经过加密、此操作将失败

从无处加载环境... 好的

在 ARM64 内核上启动 ATF……

注意:BL31:v2.10.0(发行版):b40fba1b-dirty

注意:BL31: Building:15:53:26, 2025年5月7日

I/O TC:

I/O:主 TC 初始化

I/SYSFW ABI:4.0(固件版本 0x000a '10.0.8--v10.00.08 (Fiery TC))

I/HUK:TC 已初始化

I/UL:已激活 TC 设备

I/UL:修复 GP 设备的 TC 防火墙所有者

I/TRNG:已为 SA2UL TC 器件启用防火墙

I/TRNG:SA2UL TC 已初始化

I/UL:已初始化 TC 驱动程序

I/O:主 TC 切换到正常世界引导

U-Boot SPL 2024.04-gb40fba1b-dirty (2025年5月07日- 15:54:37 +0800)

SYSFW ABI:4.0(固件版本 0x000a '10.0.8--v10.00.08 (Fiery Fox)')

检测到:J7X-BASE-CPB 版本 A

检测到:J7X-GESI - EXP 版本 E3

尝试从 MMC2 引导

警告:在 GP 设备上检测到映像签名证书。 跳过证书以防止启动失败。 如果映像也经过加密、此操作将失败

警告:在 GP 设备上检测到映像签名证书。 跳过证书以防止启动失败。 如果映像也经过加密、此操作将失败

U-Boot 2024.04-gb40fba1b-dirty (2025年5月07日- 15:54:37 +0800)

SoC:J7200 SR1.0 GP

型号:Texas Instruments J7200 EVM

板:J7200X-PM2-E6 版 SOM

DRAM:2 GiB(有效 4 GiB)

内核:114 个器件、32 个类、器件树:单独

闪存:0 字节

MMC:MMC@4f80000:0、MMC@4fb0000:1.

正在从 SPIFlash... k3-navss-ringacc ringacc@2b800000:环加速器探测环:286, gp-rings[96,32] sci-dev-id:235

k3-navss-ringacc ringacc@2b800000:dma-ring-reset-quirk:禁用

JEDEC_SPI_NOR 闪存@0:尚不支持不均匀的擦除扇区映射。

sf:检测到 s28hs512t、页面大小为 256 字节、擦除大小为 4 KiB、总共为 64 MiB

***警告 — 错误的 CRC、使用默认环境

IN:serial@2800000

输出:串行@2800000

错误:serial@2800000

am65_cpsw_Nuss 以太网@46000000:K3 CPSW:nuss_ver:0x6BA02102 cpsw_ver:0x6BA82102 ale_ver:0x00293904 Ports:1

检测到:J7X-BASE-CPB 版本 A

检测到:J7X-GESI - EXP 版本 E3

网络:eth0:以太网@46000000port@1.

按任意键停止自动引导:0

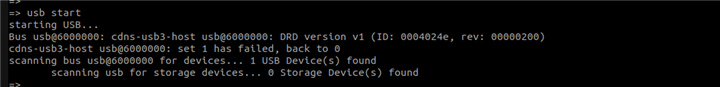

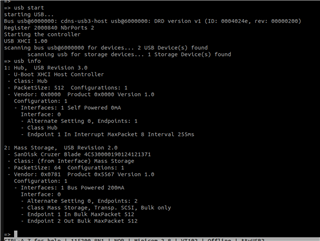

=> USB 启动

正在启动 USB...

找不到工作的控制器