工具/软件:

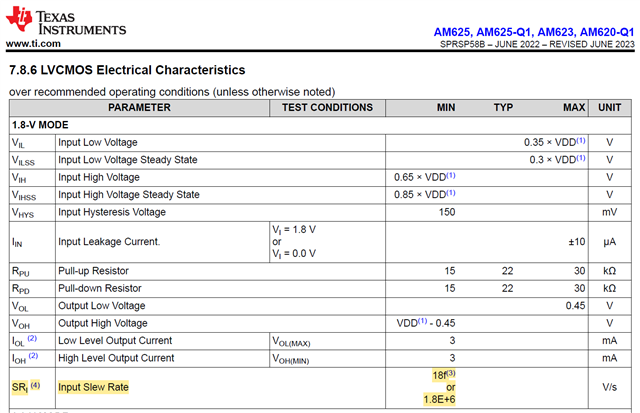

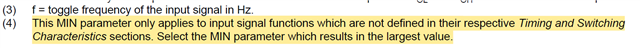

#1。 未在数据表时序部分找到 MMC0 HS200 压摆率数据、因此第 7.8.6 节 LVCMOS 电气特性数据适用?

#2. 最小值:18f 或 1.8E+6、两个值差别很大、对于 HS200、18f = 18x 200MHz、1.8E + 6 = 1.8M、这是适用于 HS200 的正确值?

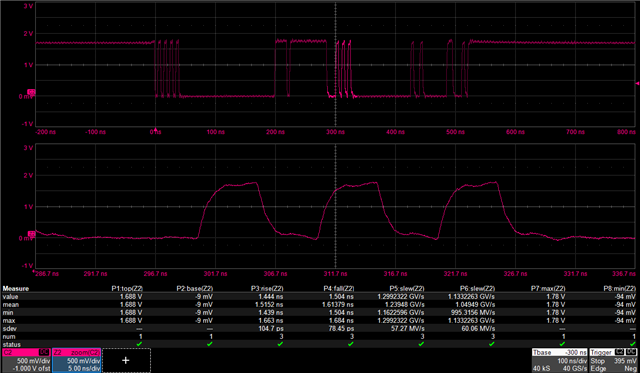

#3. 在定制电路板上、使用 eMMC 读取数据的压摆率关于 1V/ns、请参阅下图、对于上升沿和下降沿压摆率、P5 和 P6 是可以接受的、 AM62x 在 HS200 下是否可以接受?

#4. 如何指定压摆率要求? 如果压摆率较低的信号会产生什么影响?