主题:DRA821 中讨论的其他器件

工具/软件:

您好:

我将 使用 DRA821 处理器并使用文档 “slvucd4.pdf"实现“实现单 PMIC 电源方案。

我的问题是 GPIO6 的上拉电源轨。

本文档将该信号称为 EN_DDR_RET_1V1、并建议上拉电源轨为 VDD_DDR_1V1_REG。

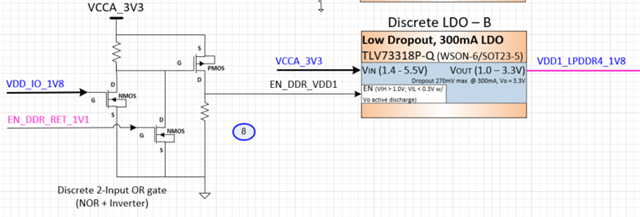

这用于使 LDO 能够提供电源轨 VDD1_LPDDR4_1V8。

这意味着 DDR 1V1 电源轨将先于 DDR 1V8 电源轨。

我认为这是一个错误。

LPDDR4 需要在 1V1 电源轨之前为 1V8 电源轨供电。

注意:我不打算在设计中使用 DDR 保持模式。

Q1/是否可以 使用电源轨 VDD_IO_1V8 (PMIC LDO1) 启用 DDR 1V8 LDO?

Q2/是否可以将电源轨 VDD_IO_1V8 (PMIC LDO1) 直接连接至 DDR4 1V8 引脚?

Q3/如何将 CPU 引脚 DDR_RET(焊球编号 R5)接通?

谢谢、

Steve