Thread 中讨论的其他器件:TDA4VH

工具/软件:

TDA4VH TRM 表明有一个 16KB L1D 分区可用作 SRAM、并独立于 L1D 高速缓存、可用于 LUT 和直方图。 这是正确的、该 SRAM 是否可以在本地用于存储标量操作数? 假设是的、我们想知道如何配置 MMU 来启用该 C7x L1D SRAM(如果存在)。 我们以 DSPLIB 环境为起点编写 C7x 代码。

- 我们在 Ubuntu 22.04.1 主机上使用 J784S4 RTOS SDK 10.01.00.04

- 我们点击以下链接、按照 DSPLIB 构建说明进行了操作: https://software-dl.ti.com/jacinto7/esd/processor-sdk-rtos-j784s4/10_01_00_04/exports/docs/dsplib/docs/user_guide/build_instructions_linux.html

- 我们已经点击此链接遵循了 CCS 裸机说明: https://software-dl.ti.com/jacinto7/esd/processor-sdk-rtos-j784s4/latest/exports/docs/psdk_rtos/docs/user_guide/ccs_setup_j784s4.html#debugging-without-hlos-running-on-a72-rtos-only-baremetal

- 我们使用 J784S4XG01EVM 修订版 PROC141E5 (001) 进行测试

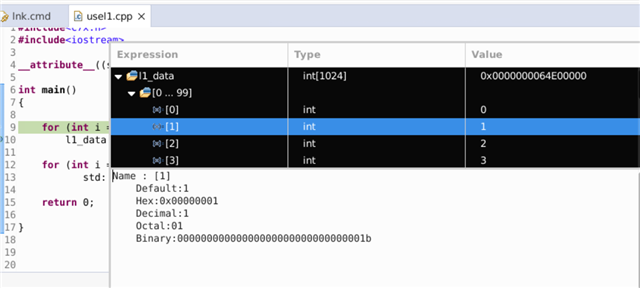

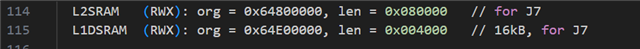

在 DSPLIB 链接器命令文件中、我们猜测 L1D SRAM 映射到地址 0x64800000、但当我们链接变量时、我们的应用程序无法正确执行、我们无法使用 CCS 修改这些地址范围。

。

。