工具/软件:

亲爱的香榭丽舍大街、

在 PRUSS_UART 中是否可以实现 24Mbps 波特率?

或者、是否可以在 PRUSS 中实现 SW UART 来实现 24Mbps 波特率?

谢谢、此致、

Si。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

亲爱的香榭丽舍大街、

在 PRUSS_UART 中是否可以实现 24Mbps 波特率?

或者、是否可以在 PRUSS 中实现 SW UART 来实现 24Mbps 波特率?

谢谢、此致、

Si。

您好、Sung-Sun IL、

硬件 UART

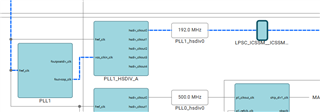

根据 AM62x 时钟树工具、硬件 UART 外设的输入时钟为 192MHz:

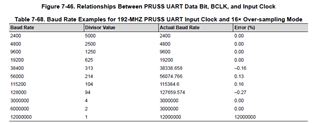

因此、如果有 8 倍过采样模式、则可以使用 24MHz (192MHz / 8)。 但是、PRU 硬件仅支持 16 倍过采样或 13 倍过采样。 因此、PRU 子系统中的硬件 UART 外设仅支持最高 12MHz 波特率。

从 AM62x 技术参考手册中、PRU > PRUSS UART

7.4.7.2.4 PRUSS UART 时钟生成和控制

PRUSS UART0 位时钟来自 PRUSS UART0 的输入时钟。 请参阅器件特定

用于检查 PRUSS UART0 支持的最大数据速率的数据表。

图 7-45 是 PRUSS UART0 的概念时钟生成图。 处理器时钟发生器

接收来自外部时钟源的信号、并通过编程产生 PRUSS UART0 输入时钟

十分之一。 PRUSS UART0 包含一个可编程波特率发生器、用于获取输入时钟并进行分频

它除以 1 到 (216-1) 范围内的除数、以生成波特时钟 (BCLK)。 BCLK 的频率为

×速率的 16 倍(×μ s)(每个接收或发送的位持续 16 个 BCLK 周期)或 13 倍 (13 μ s)

波特率(每个接收或发送的位持续 13 个 BCLK 周期)。 当 PRUSS UART0 正在接收时、

该位在第 8 个 BCLK×内× 16 μ s 过采样模式、在第 6 个 BCLK 周期内持续 13 μ s

过采样模式。 通过配置模式定义寄存器来选择 16×或 13×基准时钟:

UART_MODE[0] OSM_SEL 位。 除数的计算公式为:

分频器= UART 输入时钟频率 [MODE.OSM_SEL = 0h]

----------------------------------------

所需波特率 x 16

分频器= UART 输入时钟频率 [MODE.OSM_SEL = 1h]

----------------------------------------

所需波特率 x 13

软件 UART

为 AM335x 创建的软件 UART 的测试速率高达 115,200。 但这部分使得每个 PRU 内核能够实现多达 3 个 UART 接口、每个 PRU-ICSS 总共有 6 个额外的 UART。 文档位于此处: https://software-dl.ti.com/processor-sdk-linux/esd/docs/07_03_00_005/linux/Foundational_Components Linux_Drivers /PRU-ICSS/PRU-pru-sw-uart.html

我们目前正在研究一些较新的 PRU 器件的软件 UART 实现。 我将与团队核实我们的目标规格。 如果我在几个工作日内没有回复、请随时 ping 通该问题。

此致、

Nick

使用 AM62x 时软件 UART 的最终后续跟进:

现在、我在 AM62x 上实施的最简单的软件 UART 选项是将 AM335x 软件 UART 工程移植到 AM62x。 这样、我们就可以添加多达 6 个以高达 115,200 波特率运行的额外 UART。

有时、我想将 AM335x Linux 驱动程序和 PRU 固件移植到 AM62x、可能会在即将发布的 open-PRU 存储库中发布。 但我现在没有安排这种努力。

此致、

Nick