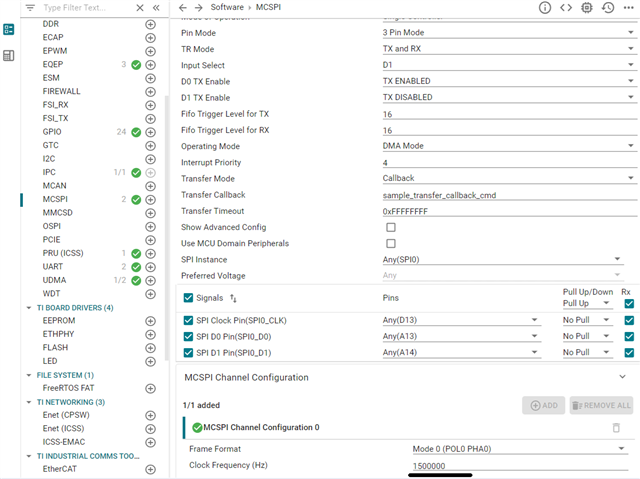

主题中讨论的其他器件:SysConfig、

工具/软件:

您好、TI 支持团队。

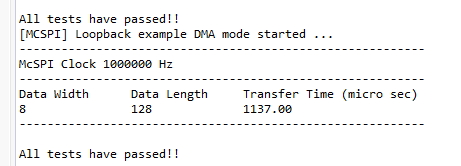

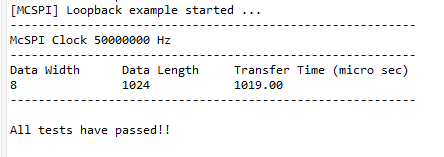

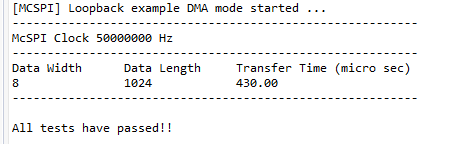

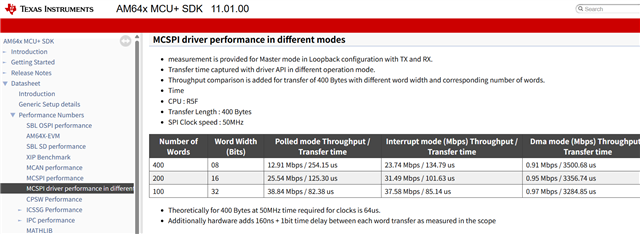

SDK 为 MCU_PLUS_SDK_am64x_08_06_00_45。

我想问一个有关 CR5 中断和 MCSPI_TRANSFER 的问题。

通过 PRU_ICSSG1_PR1_HOST_INTR_PEND_0 以 20kHz 的频率向 CR5 生成来自 PRU 的中断。

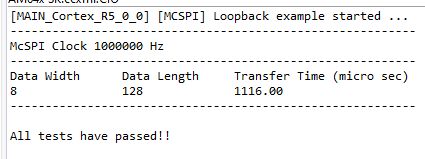

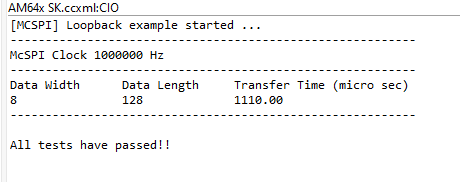

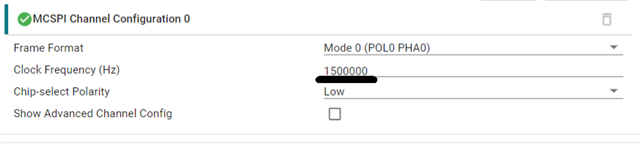

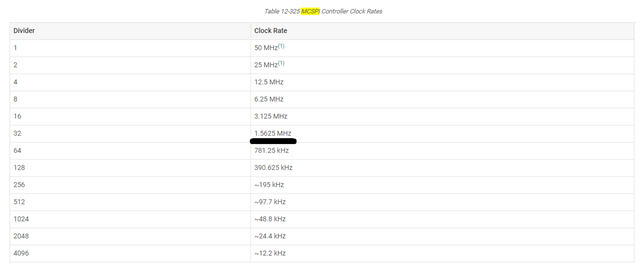

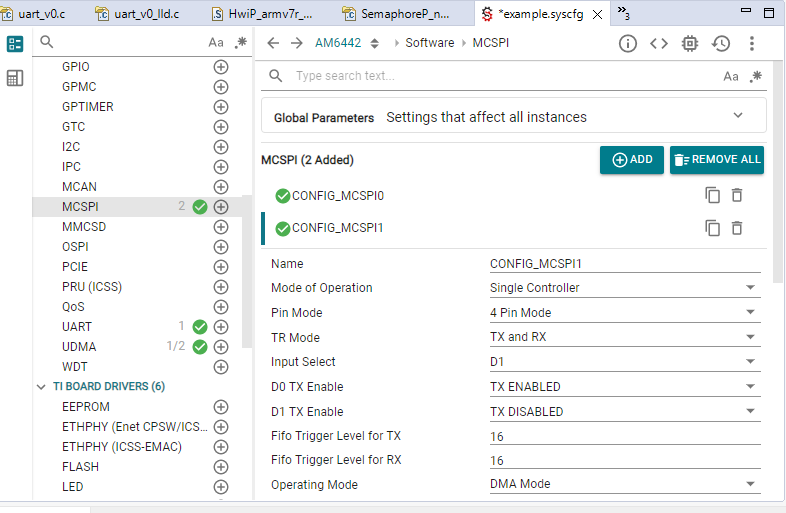

此外、在 CR5 中、使用 MCSPI_transfe 函数和计时器中断 (1kHz) 来执行 20 字节 SPI 传输。

在本例中、20kHz 处理程序的中断优先级为 1、1kHz 中断优先级为 5。

如果只有 20kHz 中断、20kHz 中断处理程序将定期调用。

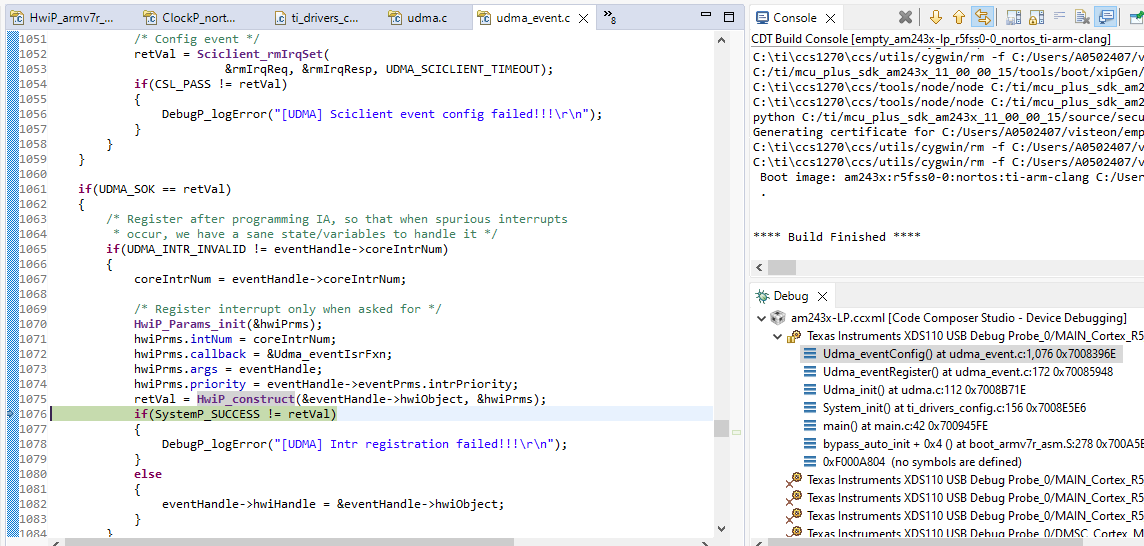

然而、如果执行 1kHz 计时器中断的 SPI 传输、则 20kHz 中断发生的时序将移位。 请参阅下图。

这可能是因为通过 MCSPI_TRANfer 禁用了中断。

我想在 SPI 传输期间定期调用 20kHz 中断处理程序、而不会禁用中断。

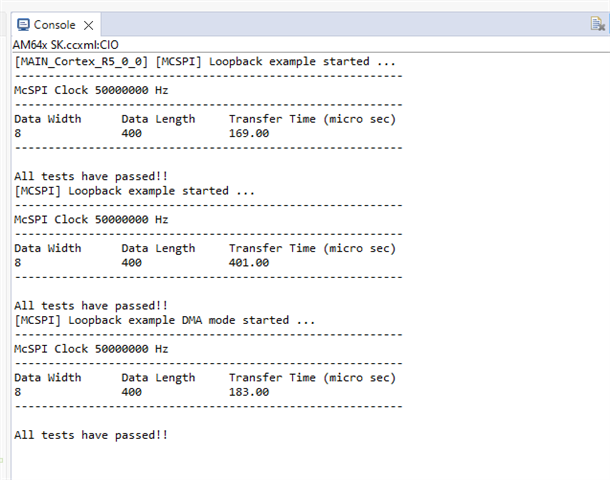

此外、MCSPI_TRANfer 的处理时间很长。

从上图可以看出、大约需要 30 μ s。

请告诉我如何解决这个问题。

此致、

今泉清正。