工具/软件:

您好:

我们正在开发 Jacinto J784s4 作为根复合体与定制 FPGA 端点之间的 PCIe 链路。

我们的用例需要在 FPGA 上使用多个 PCIe BAR。 对于某些流、我们想将一个 BAR 指定为 I/O BAR(而不是存储器 BAR)、以便让 ARM CPU 执行直接 I/O 读取/写入事务。 目标是分离流量、防止发布的事务阻止关键命令、并通过 I/O 栏确定某些控件的优先级。

查看 TRM(第 12.2.3.3.6 节)后、 我们注意到“RP 模式下的 I/O 读/写出方向“列于支持的事务中。

此外、我们对其进行了测试、并看到 IO BAR 被分配:

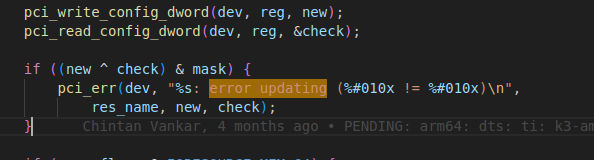

[ 0.613253] pci_bus 0000:00: root bus resource [bus 00-ff] [ 0.613259] pci_bus 0000:00: root bus resource [io 0x0000-0xffff] (bus address [0x10001000-0x10010fff]) [ 0.613263] pci_bus 0000:00: root bus resource [mem 0x10011000-0x17ffffff] [ 0.613293] pci 0000:00:00.0: [104c:b012] type 01 class 0x060400 [ 0.613298] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0x4 may corrupt adjacent RW1C bits [ 0.613406] pci 0000:00:00.0: supports D1 [ 0.613409] pci 0000:00:00.0: PME# supported from D0 D1 D3hot [ 0.615349] pci 0000:00:00.0: bridge configuration invalid ([bus 00-00]), reconfiguring [ 0.616014] pci 0000:01:00.0: [10ee:9034] type 00 class 0x058000 [ 0.620254] pci 0000:01:00.0: reg 0x10: initial BAR value 0x00000000 invalid [ 0.620258] pci 0000:01:00.0: reg 0x10: [io size 0x8000] [ 0.620281] pci 0000:01:00.0: reg 0x14: [mem 0x00000000-0x001fffff] [ 0.641938] pci_bus 0000:01: busn_res: [bus 01-ff] end is updated to 01 [ 0.641957] pci 0000:00:00.0: BAR 14: assigned [mem 0x10200000-0x103fffff] [ 0.641962] pci 0000:00:00.0: BAR 13: assigned [io 0x8000-0xffff] [ 0.641966] pci 0000:01:00.0: BAR 1: assigned [mem 0x10200000-0x103fffff] [ 0.646188] pci 0000:01:00.0: BAR 0: assigned [io 0x8000-0xffff] [ 0.646235] pci 0000:01:00.0: BAR 0: error updating (0x10009001 != 0x10008001) [ 0.653446] pci 0000:00:00.0: PCI bridge to [bus 01] [ 0.653451] pci 0000:00:00.0: bridge window [io 0x8000-0xffff] [ 0.653458] pci 0000:00:00.0: bridge window [mem 0x10200000-0x103fffff] [ 0.653524] pcieport 0000:00:00.0: of_irq_parse_pci: failed with rc=-22 [ 0.660132] pcieport 0000:00:00.0: enabling device (0000 -> 0003) [ 0.660306] pcieport 0000:00:00.0: PME: Signaling with IRQ 407 [ 0.660467] pcieport 0000:00:00.0: AER: enabled with IRQ 407 [ 0.660735] j721e-pcie 2910000.pcie: host bridge /bus@100000/pcie@2910000 ranges: [ 0.660752] j721e-pcie 2910000.pcie: IO 0x0018001000..0x0018010fff -> 0x0018001000 [ 0.660762] j721e-pcie 2910000.pcie: MEM 0x0018011000..0x001fffffff -> 0x0018011000 [ 0.660772] j721e-pcie 2910000.pcie: IB MEM 0x0000000000..0xffffffffffff -> 0x0000000000 [ 1.664195] j721e-pcie 2910000.pcie: PCI host bridge to bus 0001:00 [ 1.664201] pci_bus 0001:00: root bus resource [bus 00-ff] [ 1.664206] pci_bus 0001:00: root bus resource [io 0x10000-0x1ffff] (bus address [0x18001000-0x18010fff]) [ 1.664210] pci_bus 0001:00: root bus resource [mem 0x18011000-0x1fffffff] [ 1.664230] pci 0001:00:00.0: [104c:b012] type 01 class 0x060400 [ 1.664235] pci_bus 0001:00: 2-byte config write to 0001:00:00.0 offset 0x4 may corrupt adjacent RW1C bits [ 1.664347] pci 0001:00:00.0: supports D1 [ 1.664350] pci 0001:00:00.0: PME# supported from D0 D1 D3hot [ 1.666280] pci 0001:00:00.0: bridge configuration invalid ([bus 00-00]), reconfiguring [ 1.666397] pci_bus 0001:01: busn_res: [bus 01-ff] end is updated to 01 [ 1.666410] pci 0001:00:00.0: PCI bridge to [bus 01] [ 1.666462] pcieport 0001:00:00.0: of_irq_parse_pci: failed with rc=-22

我们的问题是:

- 在 Jacinto J784S4 上、是否可以实际对 PCIe 端点 (FPGA) 上的 I/O 栏执行读取/写入访问?

- 如果没有、是否有任何硬件或软件权变措施(设备树,内核,配置)来启用此功能?

- 如果无法做到这一点、您能否确认只有内存条 (MEM) 可真正访问?

非常希望提供有关 SoC 限制的任何文档指导或详细说明。

非常感谢您的帮助!

此致、

K.Luong