Thread 中讨论的其他器件: ADS127L18、SysConfig、 TMDS64EVM

工具/软件:

尊敬的 TI 专家:

我们有以下硬件配置:

这两个 ADC 在 AM6442 SoC 上的多控制器模式下连接到 McSPI4、并要在 R5F 侧使用。 要求如下:

- 128KSPS 读取速率

- 顺序读取、首先是 ADC1、然后是 ADC2。 我们必须能够区分数据源、即样本是否来自 ADC1 或 ADC2

- 稳定的读数频率 — 最大 抖动 10ns

- 每 32 个样本中断一次

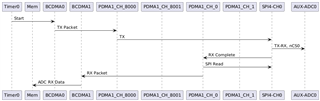

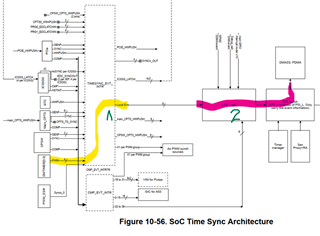

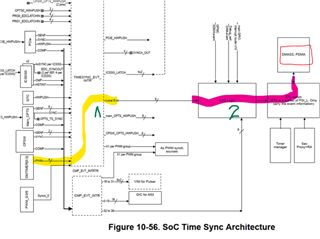

我们已经有另一个 ADC 连接到 SoC (8 通道 ADS127L18)、它充当 SPI 主器件、并在外设模式下为 2 个 McSPI 生成 nCS 和时钟。 该 ADC 通过 PKTDMA+PDMA 读出、并在 McSPI RX 上触发。

我们的目的是使用从 ADS127L18 生成的 nCS(在内部,作为内部触发器,或在外部用作 GPIO 中断)、或使用计时器触发第二个 DMA(它必须按顺序读取两个 ADC)。

请注意、此处不能选择计时器中断、因为它会导致大量抖动、从而导致数字化信号失真。 我们需要稳定的读数频率。

我们有以下问题:

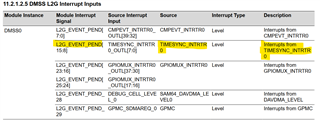

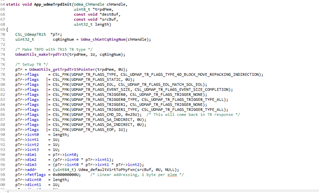

- 显然、PKTDMA 不能从任意触发源触发;它必须是从外设生成的数据包/事件。 这意味着我们必须使用 BCDMA、对吧? 使用 BCDMA 是否与用于 McSPI 的 PDMA 兼容?

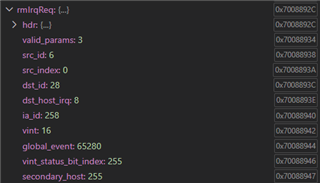

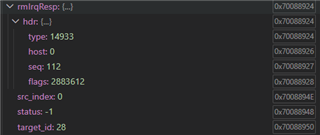

- 将 BCDMA 配置为使用内部信号(例如来自另一个 McSPI(例如 McSPI 3) 的)的 RX complete) 的方法是什么?哪个信号用于触发来自另一个 McSPI 的 DMA 传输?

- BCDMA 必须配置为依次读取 ADC、ADC1 和 ADC2、因为它们共享相同的 McSPI。 理论上、这些是 2 个独立的 SPI 通道、但可以通过以下方式链接 DMA:

- 外部事件(ADS127L18 nCS、GPIO 中断或计时器)会触发 ADC1 的读取

- 完成后、ADC1 的 McSPI TX 完成会触发 ADC2 读取

- 我们是否可能需要多个 BCDMA 通道才能实现上述目标?

谢谢!