工具/软件:

您好:

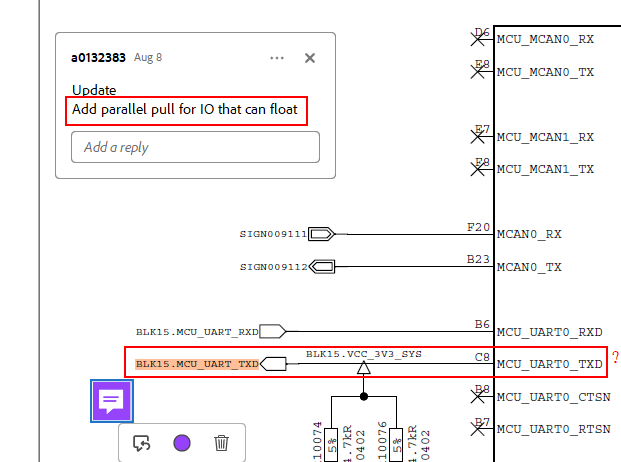

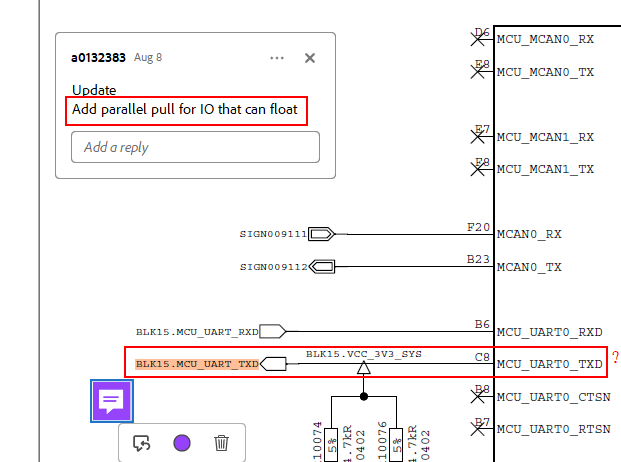

如下所示、在 TI 审查我们的应用原理图时、给出了一些注释、但在这里、我不太清楚“为可以悬空的 IO 添加并联拉电阻“。 是否意味着如果此引脚未在应用中使用、则需要为此引脚添加外部上拉/下拉电阻器? 并且使用这个引脚时无需外部拉电阻、对吧? 谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好:

如下所示、在 TI 审查我们的应用原理图时、给出了一些注释、但在这里、我不太清楚“为可以悬空的 IO 添加并联拉电阻“。 是否意味着如果此引脚未在应用中使用、则需要为此引脚添加外部上拉/下拉电阻器? 并且使用这个引脚时无需外部拉电阻、对吧? 谢谢!

你好、 Liujian Zhang

感谢您发送原理图审阅申请。

UART0_TXD0

对于 LVCMOS IO、缓冲器在复位期间和复位后关闭。

在 SOC 将 IO 配置为输出和/或启用上拉电阻之前、TX 不会驱动所连接器件输入。

如果在处理器配置 IO 之前、所连接器件输入悬空、建议添加外部拉电阻。

对于任何连接了布线但未主动驱动的 SOC IO、都是如此。

https://www.ti.com/lit/an/spradn4a/spradn4a.pdf

5.2.1.2 并联拉电阻

建议为向具有布线的处理器 IO 添加并联拉电阻提供配置

已连接且未被主动驱动、或用于连接到可悬空的所连接器件输入的 IO

(防止所连接器件输入悬空直到由主机驱动)。 并行拉电阻极性和拉电阻值

根据具体的外设连接建议、对改进处理器的建议

性能和可靠性以及相关接口或接口标准要求。

处理器特定 SK 中使用的拉电阻值可用作起点、定制电路板设计人员可以选择

基于处理器和连接器件或特定的建议的适当拉电阻值

设计要求。

当布线连接到处理器引脚(IO 焊盘)并且 IO 未被主动驱动(悬空)时、

建议使用并联拉电阻。 在复位期间和复位后处理器 IO 缓冲器关闭。 IO 处于高电平

阻抗状态、实际上相当于可以拾取噪声的天线。 在不并联拉电阻的情况下、IO

处于高阻抗状态。 高阻抗使得噪声可以轻松地将能量耦合到悬空信号布线上

并产生可能超出 IO 建议工作条件的电位。 电势会产生一个

IO 上的电过应力 (EOS)。 处理器内部的静电放电 (ESD) 保护电路

设计用于在处理过程中、仅在将器件安装到 PCB 上之前保护器件免受 ESD 影响

此致、

Sreenivasa.

你好、 Liujian Zhang

谢谢你。

我不确定我是否理解第一个问题。 我会尽力回答。 请详细说明问题、以防我的理解不正确。

]“ 复位期间和复位后处理器 IO 缓冲区关闭“的影响是什么? 如果 IO 缓冲器可由 SW 设置为“On"?“?

当 TX 和 RX 缓冲器关闭时、IO 处于高阻态。

软件启动后、软件可以启用内部拉电阻和 IO 缓冲器。

对于驱动强度、可以配置 SDIO 和 LVCMOS、对吧? [/报价]我们目前不支持配置驱动强度。

我们在内部评估支持驱动强度配置。

这是配置驱动强度的用例吗?

此致、

Sreenivasa.