工具/软件:

你(们)好

我还有一个问题

在上述主题中、客户询问了断开 MMC0 时的引脚手环。

因为如果 VDDS_MMC0 的连接和 1.8V 模拟连接(例如 VDDA_ADC、VDDA_MCU 或 VDDS_OSC)导致 SoC 中的模拟 IP 出现一些噪声、则这些值会出现担忧。

然后、我们得到的答案为

“通过适当的系统实施、可以在共享电源上组合数字负载和模拟负载、但为数字负载和模拟负载创建单独的电源将降低与数字负载在模拟电源轨上产生噪声相关的风险。 系统设计人员需要 使用适当的去耦电容器和 PCB 布局、以尽可能地降低共享电源上的噪声。 “

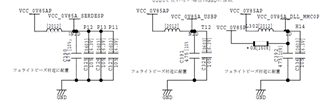

他们查看了 TI EVM、并设计了 0.85V 模拟电源系统、以按如下方式隔离电源引脚:

同样、带有铁氧体磁珠和电容器的 π μ F 型滤波器设计用于将 VDDS_MMC0 与 1.8V 模拟电源分开。

它们的用例如下。

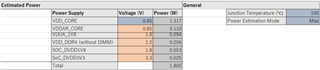

| MHz | 利用率百分比 | |

| 1xA53 | 1000 | 100% |

| 2xR5F | 800 | 100% |

| 1xM4F | 400 | 100% |

| 2xUART | 12Mbps | 100% |

| 2 个 SPI | 1.563 个字节 | 100% |

| OSPI | 160Mbd | 30% |

| DDR4 | 1600 | 100% |

| PCIe | 第 2 代 | 100% |

此用例的估算功耗为

您 π 将 VDDS_MMC0 和 1.8V 模拟系统与此 μ F 类型滤波器分开是否足以满足其用例需求?

他们不希望 TI 保证它能正常工作。

他们希望获得 TI 的建议、无论噪声风险是足够高还是足够低。

谢谢、此致、

Tsurumoto。