工具/软件:

您好:

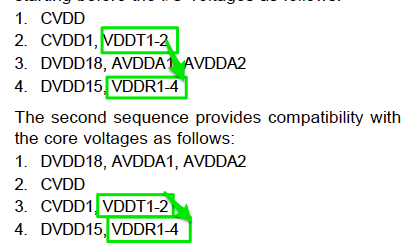

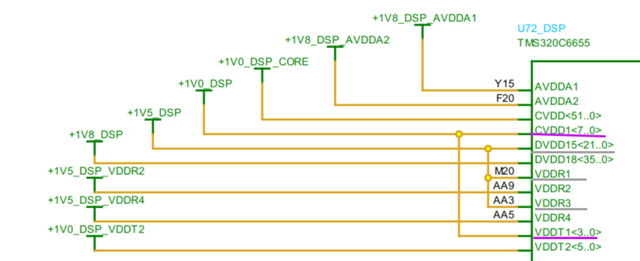

我在 TMS320C6655 上进行 SW 加载时遇到问题、这促使我研究了器件的复位和电源序列。

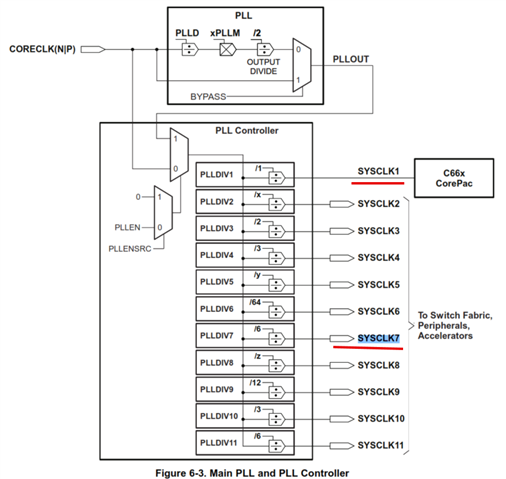

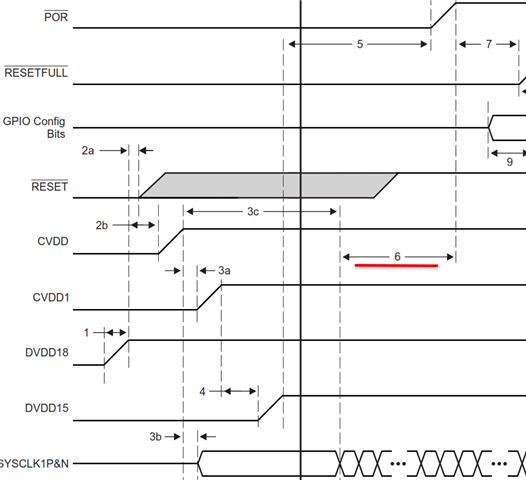

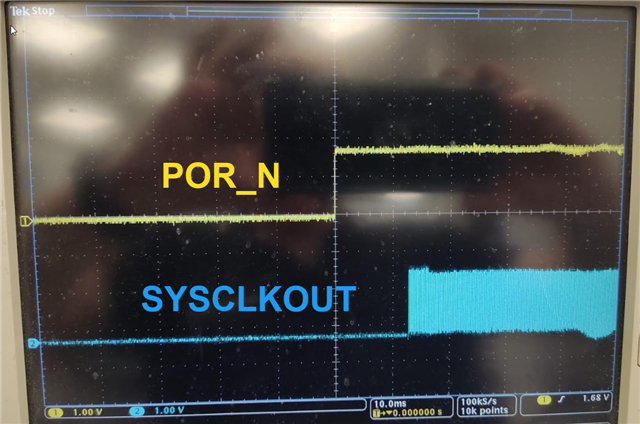

根据数据表、只有在 SYSCLK1 已稳定后、POR_N 才应变为高电平:

![]()

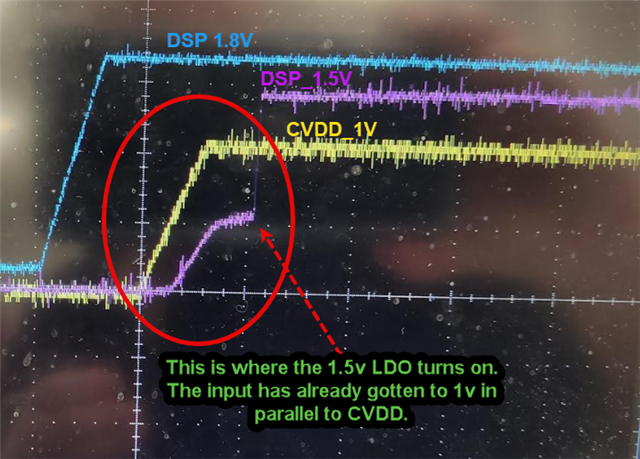

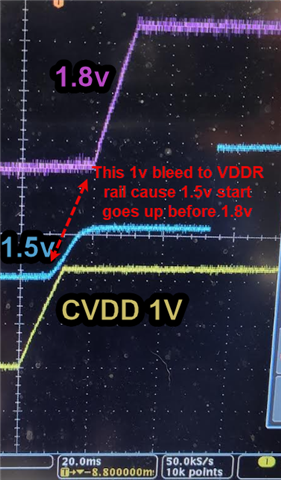

现在、我将在实验室中对其进行测试。 我根据数据表以正确的顺序拉高 Resets(第一个:RESET_N、第二个:POR_N、第三个:RESETFULL_N)、并且只有在所有电源轨都已经处于高电平 (CVDD、CVDD1、1.8、1.5) 后、所有这些电源轨才会被拉至高电平。

从一些不清楚的原因来看、我可以看到 SYSCLKOUT (7) 只有在 POR_N 被拉高后才会稳定、不管我在 RESET_N 到 POR_N 之间延迟了多少时间

您能否澄清为什么会发生这种情况?

Ohad