工具/软件:

尊敬的 TI 团队:

我们目前正在使用设计定制电路板 AM62L 软件 LPDDR4 并且注意到 LPDDR4 信号布线的阻抗要求存在差异。

-

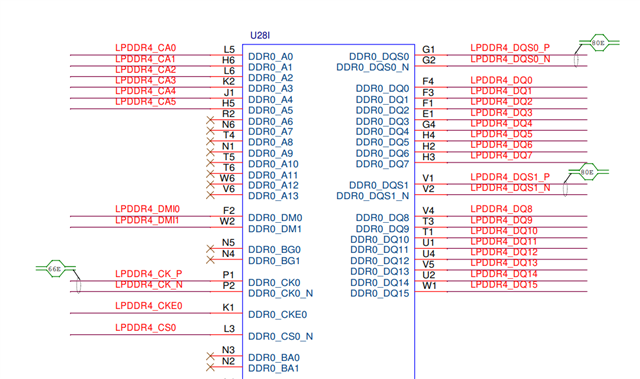

在中 EVM 原理图 、指定的阻抗为:

-

66Ω 指定

LPDDR4_CK_P/N -

80Ω 指定

LPDDR4_DQSx_P/N

-

-

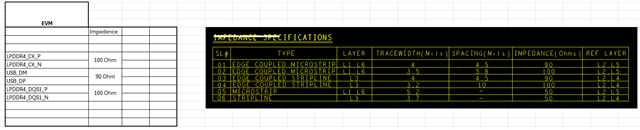

不过、在中 EVM 布局 、路由如下:

-

100Ω 差分

-

50Ω 单端

-

-

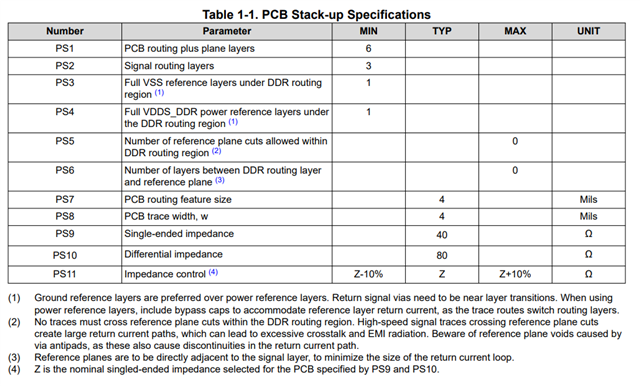

在中 LPDDR4 布线指南 文档中、建议:

-

80Ω 差分

-

40Ω 单端

-

我们随附了原理图、布局和布线指南文档的屏幕截图、以供您参考。

您能否请确认为我们的定制电路板应遵循哪些阻抗值、从而确保信号完整性。

期待您的指导。

此致、

Jaydip