Thread 中讨论的其他器件:TDA4VH

工具/软件:

当 REFCLK 用作从 TDA4VH SoC 到外设的输出时、PCIe REFCLK_P/REFCLK_N 上的 50 Ω 终端电阻器的建议放置方式是什么?

我们正在使用 Hyperlynx 仿真 PCIe REFCLK、并使用标准 SERDES 模型生成 100MHz 差分时钟。

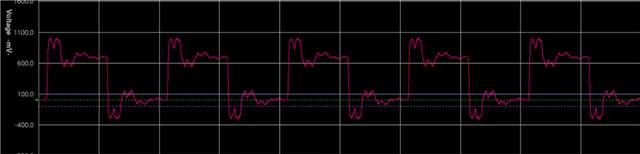

按照 Jacinto7 AM6x、TDA4x 和 DRA8x 高速接口 (spracp4a) 和 TDA4VH EVM 设计的建议、将 50 欧姆终端电阻放置在靠近 SoC 的位置时、我们会得到以下信号波形:

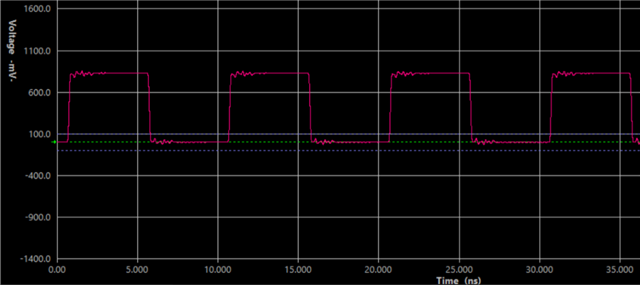

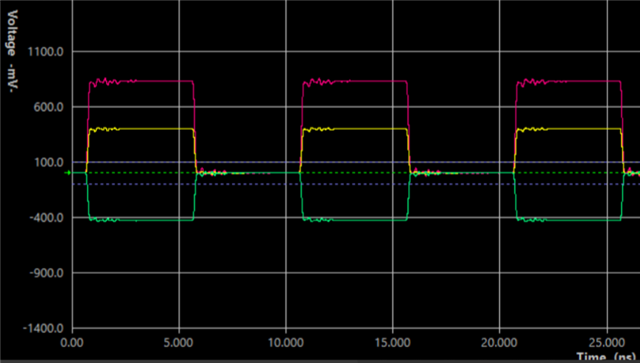

但是、当从靠近 SoC 的位置移除端接电阻器并将其放置在外设(接收器)旁边时、我们会得到以下信号波形、这看起来更像预期的波形。

在这种情况下、TDA4VH PCIE_REFCLK 输出是否不同、终端电阻器仍应靠近 SoC(发送器)、而不是靠近外设(接收器)?

如果是、您是否会有仿真模型 pcie_refclk?