Thread 中讨论的其他器件:AM69

工具/软件:

您好、

因为如果在启动期间配置为 Gen3、则可能无法识别外部开关芯片、从而导致驱动器加载失败。 因此、Gen2 在启动期间默认为高电平。 是否有办法在 TDA4 启动后将 PCIe 速率从第 2 代修改为第 3 代?

此致、

Yang

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、

感谢您的耐心。 答案很简单:是的、PCIe 控制器支持在启动后将链路重新训练至不同的速度。 这可以通过写入某些寄存器来完成、例如 pcie_core_RP_I_LINKWIDTH_CONTROL_REG 或 pcie_core_LM_I_LINKWIDTH_REG_REG(取决于您访问 PCIe 控制器的方式以及控制器所处的角色)。

有关这些寄存器的信息可以在 TDA4 DRA829TDA4VM_DRA829TDA4VM_CCS Registers_Part4.pdf(可以在此处下载 www.ti.com/.../TDA4VM 4 部分中找到 。 有关上述这些特定寄存器的信息、可在以下 pdf 中找到:第 1725 页的 LM 寄存器和第 2254 页的 RP 寄存器。

我希望这对您有所帮助! 如果您有任何其他问题、请告知我们。

此致、

Jeff

您好、

这还取决于您所操作的系统。 例如、如果您使用 Linux、以下顺序应该适用:

setpci -s 0000:00:00.0 CAP_EXP+0x30.W=0x3 — 通过设置链路控制 2 寄存器、可将目标链路速度更改为第 3 代速度

setpci -s 0000:00:00.0 CAP_EXP+0x10.0.W=0x20 — 这通过设置链路控制寄存器的位 5 来重新训练链路

lspci -vv -s 0000:00:00.0 | grep -i speed — 读取设置为目标速度和实际速度的速度

总线号“0000:00:0.0"将“将取决于您的硬件。 您可以使用 lspci 命令检查枚举的内容。

请告诉我们这是否有帮助、或者您用于操作控制器的系统。 谢谢!

此致、

Jeff

您好、

我刚刚在 AM69 上进行了实验、想看看我是否可以将链路重新训练到比 lnkcap 寄存器中广播的速度更高的速度。 初次尝试时、似乎链接速度高达 8GT/s。 问题可能在其他地方。

在再培训期间、这可能是一个均衡阶段问题。 您能否检查 PCIe 配置空间中的 LnkSta2 寄存器以判断某些均衡相位是否通过。

此外、许多 PCIe 问题源自时钟问题、因为根端口和端点都需要正确同步以避免问题。

什么是时钟配置、即 REFCLK?

J7 和 PCIe 端点的源是什么?

他们有共享时钟吗?

是外部时钟、还是由 J7 通过其 PLL 在内部配置?

此致、

Jeff

您好、

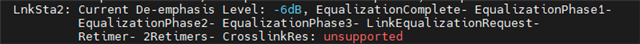

以下是关于 LnkSta2 的信息:

什么是时钟配置、refclk?

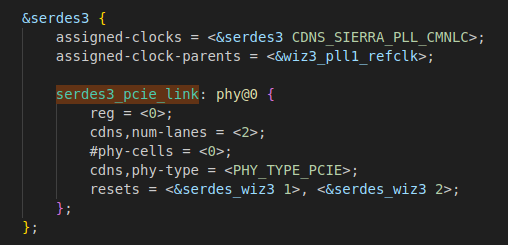

是、当前 REFCLK 是 TDA4 中的默认 REFCLK。

J7 和 PCIe 端点的源代码是什么?

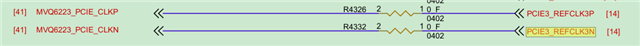

EP 是一种 MVL 开关。

[报价 userid=“656581" url="“ url="~“~/support/processors-group/processors/f/processors-forum/1544420/tda4vm-modify-pcie-speed-from-gen2-to-gen3-after-tda4-startup/5978736他们有共享时钟吗?

是外部时钟、还是由 J7 通过其 PLL 在内部配置?

[/报价]J7 内的 PLL 配置的时钟。

此致、

Yang

您好、

嗯、链路均衡似乎失败、或者甚至可能从未启动。 均衡开始时、链路必须处于 L0 状态。 您是否熟悉 PCIe 控制器的 TI 寄存器读数? 如果是、则有一个寄存器保存 LTSSM 所处状态的值。 我很想知道在均衡开始时链路是否处于正确的 L0 状态。 如果您可以找到控制器基地址、LTSSM 寄存器偏移位于该寄存器的位 29:24 中。 这将告诉您链路的状态。 设置新速度后、设置再训练位之前、能否读取该寄存器/存储器?

此致、

Jeff

您好、

感谢您的屏幕截图。 我想更深入地探讨猛虎组织的状况。 您能否以足够高的频率轮询 LTSSM 字段 (PL_CONFIG_0 的位 29:24)、以便在重新训练初始化后捕获 LTSSM 的所有瞬态状态变化?

此外、如果可以屏蔽这些寄存器位(移位并清零不需要的位)、那么更容易看到实际的 LTSSM 状态位域结果。

基本上、一旦您初始化为 Gen3、就开始轮询 LTSSM 状态寄存器来查看它是如何从状态转换到状态的。

此致、

Jeff

您好、

下面是指向具有轮询 LTSSM 状态的详细信息的线程的链接。 它还包含一个 bash 脚本来执行此操作。

【常见问题解答】AM69:TDA4VH 如何检查当前 PCIe LTSSM 状态?

此致、

Jeff