工具/软件:

全部、

我指定的 Focus 客户对 MMC0 速度有疑问:

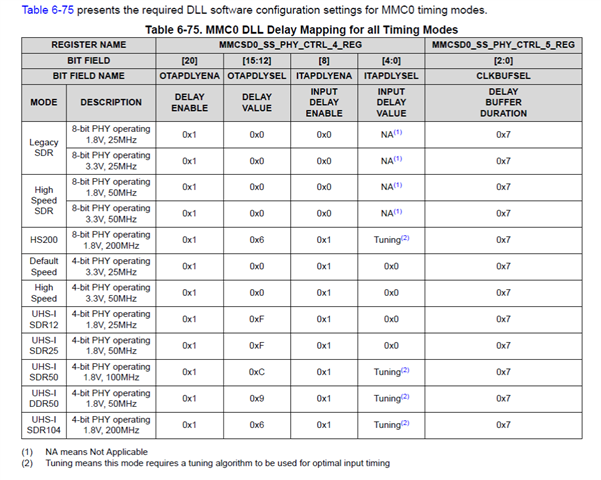

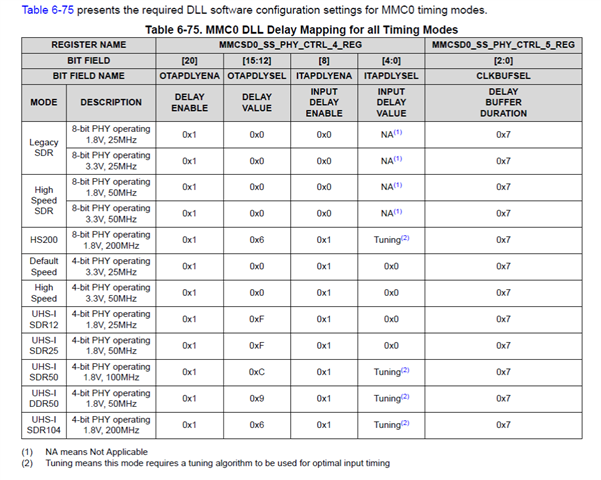

是否支持高达 50MHz 的 DDR 模式(4 位、8 位)? 根据下表、我们在 3.3V 下能够最快实现的似乎是 8 位的 52MHz。

请提供建议。

我要求澄清他的目标。 我假设这是可能的最快速度。 这是否是 200MHz 的 HS200 8 位、而不是上面提到的 3.3V @ 50MHz?

此致、

Blake

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

全部、

我指定的 Focus 客户对 MMC0 速度有疑问:

是否支持高达 50MHz 的 DDR 模式(4 位、8 位)? 根据下表、我们在 3.3V 下能够最快实现的似乎是 8 位的 52MHz。

请提供建议。

我要求澄清他的目标。 我假设这是可能的最快速度。 这是否是 200MHz 的 HS200 8 位、而不是上面提到的 3.3V @ 50MHz?

此致、

Blake

我看到还有更多的问题,我错过了:

我对 MMC0 接口有几个问题、这是我们将用于 eMMC NAND 闪存的接口。 我们计划在 DDR 的 52MHz 运行该工具。

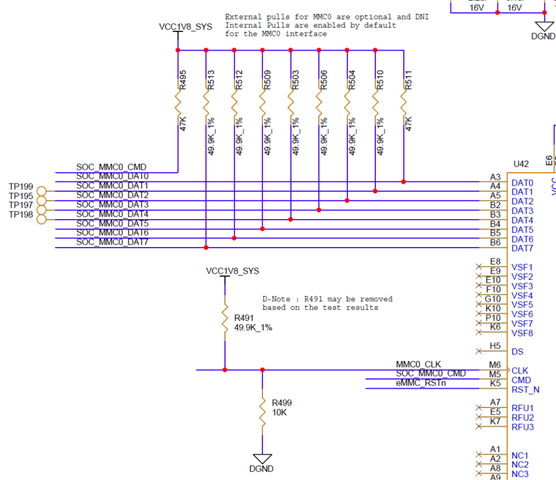

2.另外, EVB 原理图有一些关于 eMMC0 接口及其内部拉电阻的注释。

您插入的表格中的任何位置均未提及 52MHz。 由于 AM62Lx PLL 工作频率和 内部时钟分频器、在 eMMC 标准中、我们仅在定义为在 52MHz 下运行的模式下支持高达 50MHz 的电压。 eMMC 标准不允许通过 52MHz 运行的任何模式发出 3.3V 信号。 因此、HS200 在 1.8V 下运行。

您插入的表 将在数据表的下一个版本中更新。 我们将为“高速 DDR“添加新行、其中包括 1.8V 或 3.3V 的工作电压、但在此模式下、频率将限制为 40MHz。 我们还删除了表中的最后三行。 之所以这样做、是因为 AM62Lx MMC0 端口仅支持 eMMC 和嵌入式 SDIO。 它不支持 SD 卡、 嵌入式 SDIO 器件仅在高达 UHS-I SDR25 的速率下运行。

在 MMC0 信号功能上实现的 SDIO 缓冲器类型具有固定的 40 Ω 源阻抗。

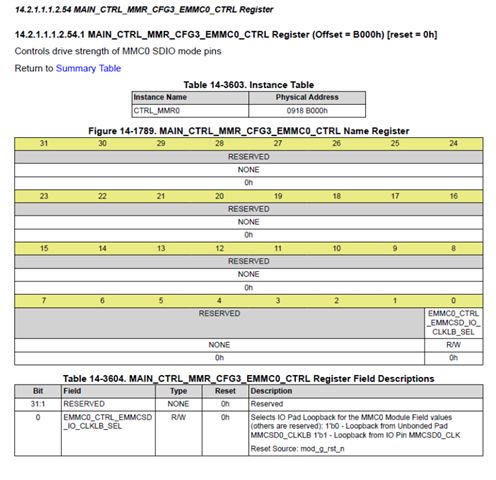

对于 AM62Lx、您插入的原理图快照看起来不正确。 当连接到 eMMC 器件时、AM62Lx MMC0 信号的建议外部拉电阻 为 CLK 上的下拉电阻、CMD 上的上拉电阻和 DAT0 上的上拉电阻。 我建议使用标准容差 47k Ω 电阻器。 需要使用这些拉电阻来在未受保护的 eMMC 输入上保持有效的逻辑状态、直到软件初始化 MMCSD0 主机控制器和相关的 IO、因为默认情况下会关闭与这些信号关联的 AM62Lx IO。 默认情况下、eMMC 标准要求所有 eMMC 器件通过打开内部上拉电阻器来为其 DAT[7:1]输入提供内部保护。 进入 8 位模式时、eMMC 器件将关闭 DAT[7:1]上的内部上拉电阻、或者 在进入 4 位模式时关闭 DAT[3:1]上的内部上拉电阻。 当 eMMC 器件关闭这些信号上的内部上拉电阻时、主机应该打开这些信号上的内部上拉电阻。 因此、 DAT[7:1]不需要外部上拉电阻。 不过、我们最近发现 TI 软件没有为这些信号开启主机上拉电阻器、这意味着这些信号 在未驱动时悬空。 我假设这将在新版本的软件中得到修正。

此致、

Paul

您好 Blake、

添加其他信息供您查看

SK 设计文件:

在 上一修订版中观察到一些差异。

所有必需的更新都是最近进行和发布的。

SPRCAL6B.ZIP (97010 KB)

有关原理图的快速参考、请参阅以下链接:

我们嵌入了包含组件详细信息的标准 PDF 和智能 PDF。

这些 EVM 已使用原理图配置进行了测试。

关于上面提供的原理图图片:

E2E 中发布的原理图似乎是客户原理图。

似乎客户重复使用了 SK 的原理图、没有重新配置 DNIS。

我们在硬件设计注意事项文档中提供了此注释:

当重复使用 SK 设计(原理图)时、可以复位所有元件的 DNI 设置。 请确保重新配置 DNI(安装 DNI 可能会影响功能)。

https://www.ti.com/lit/pdf/sprujc9

此致、

Sreenivasa.

您好、Paul:

我们处于竞争劣势、因为它们空间受限并连接到 3.3V。 80Mbps 与 104Mbps。 您看到了任何选项吗?

以下是我与客户的讨论:

那么、您正在查看 SDR 50MHz 8 位且频率为 3.3V 的正确值吗? 【客户】正确、但根据当前信息、我宁愿选择当前支持的 40MHz DDR、8 位、3.3V(根据 Paul 之前的回答)、因为这会提高吞吐量。

那么、如果您可以在 8 位/3.3V 下执行 DDR 50MHz 或 SDR 100MHz、以便使速度加倍并避免电平转换器正确吗? 【注意:这些选项目前不是已发布的选项,但我想追逐为什么以及它们是否可以成为有效的选项,但我想健全地检查它们是否能首先解决您的问题】。 【客户】是的、100MHz 8 位/3.3V 的 SDR 理论上可以解决我的问题。 实际上、这不会解决我的问题、因为它不是 eMMC 规范的一部分、因此您找不到支持该功能的 eMMC 器件 (100MHz 为 8 位、3.3V 的 SDR)。

此外、200MHz ~会使电流吞吐量增加一倍、但代价是如果使用电平转换器降至 1.8V、则会占用您不需要的空间。 对吧? 【您已使用之前的电子邮件删除此选项–但我想确保我理解正确】。 【客户】正确。

以下说明的 40MHz 3.3V DDR 如何?:

您插入的表将在数据表的下一个版本中更新。 我们将为“高速 DDR“添加新行、其中包括 1.8V 或 3.3V 的工作电压、但在此模式下、频率将限制为 40MHz。 我们还删除了表中的最后三行。 之所以这样做、是因为 AM62Lx MMC0 端口仅支持 eMMC 和嵌入式 SDIO。 它不支持 SD 卡、嵌入式 SDIO 器件仅在高达 UHS-I SDR25 的速率下运行。

这将给你一个有效的 80 而不是 104 但比 50 更好. 这是您正在考虑的选项吗? 【客户】是的、这是我计划使用的选项、因为它是我们当前情况下的最佳实用选项。

他是否在使用我们的最佳选择?

谢谢、

Blake

您好、Paul:

客户询问:

TI 能否确认该软件问题已得到解决? 如果已修复、我将从 MMC0 数据线 (D1..D7) 上移除 47k 上拉电阻器:

[Paul 写入]因此、 DAT[7:1]不需要外部上拉电阻器。 不过、我们最近发现 TI 软件没有为这些信号开启主机上拉电阻器、这意味着这些信号 在未驱动时悬空。 我假设这将在新版本的软件中得到修正。

如果尚未修复、TI 何时预计会完成此操作? Itron 将使用 TI 的驱动程序(裸机和 Linux)、因此我假设您的驱动程序中没有修复、那么无论我们使用的是什么、都不会修复。

建议客户在裸机/Linux 的原理图中做些什么? 谢谢!

此致、

Blake